Fixed point vector processor and vector data access controlling method thereof

A vector processor and data control technology, applied in the direction of machine execution devices, etc., can solve the problems of low versatility, low computing performance, high power consumption and delay, etc., to achieve enhanced reusability, improved computing performance, and flexible configuration. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

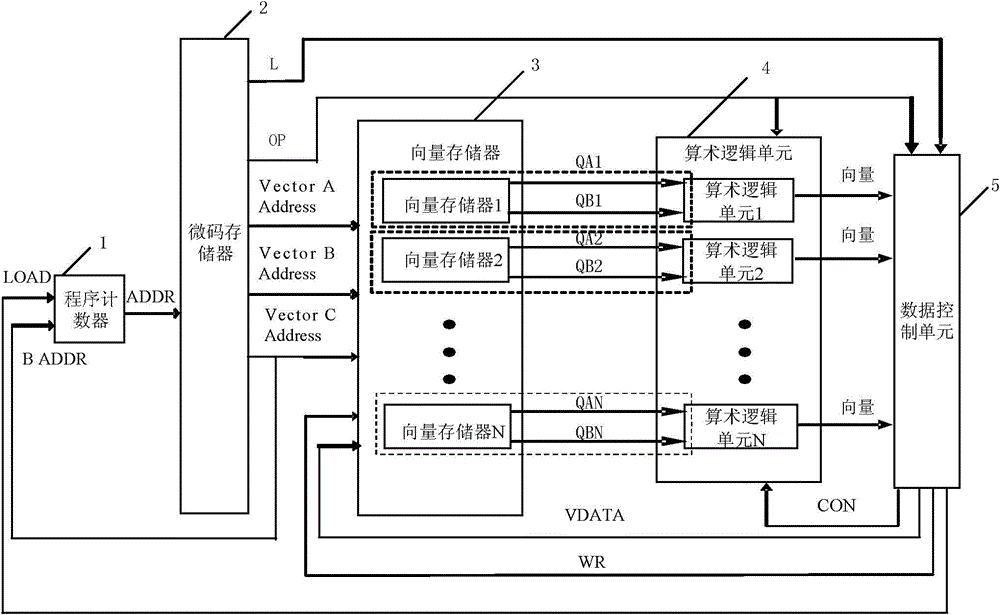

[0028] Specific implementation mode 1, refer to figure 1 Specifically illustrate the present embodiment, the fixed-point vector processor described in the present embodiment, it comprises program counter 1, microcode memory 2, vector memory 3, arithmetic logic unit 4 and data control unit 5;

[0029] The program counter 1 is used to receive the counting instruction sent by the data control unit 5 and the input target address microcode instruction sent by the microcode memory 2, and output the count value to the microcode memory 2;

[0030] The microcode memory 2 is used to receive and store the count value sent by the program counter 1, and output the path index L microcode instruction to the data control unit 5, and simultaneously output the OP microcode instruction to the arithmetic logic unit 4 and the data control unit 5, and output the input Vector address microcode instructions to vector memory 3, output and input target address microcode instructions to program counter ...

specific Embodiment approach 2

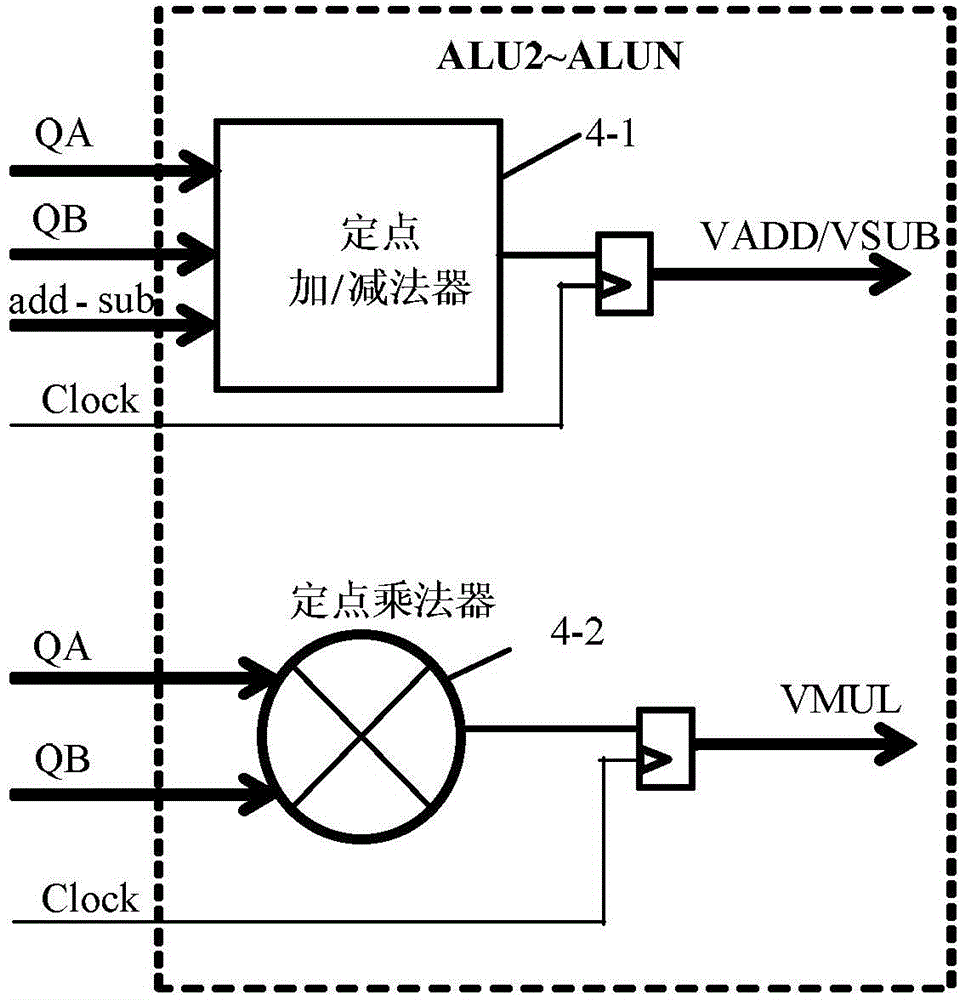

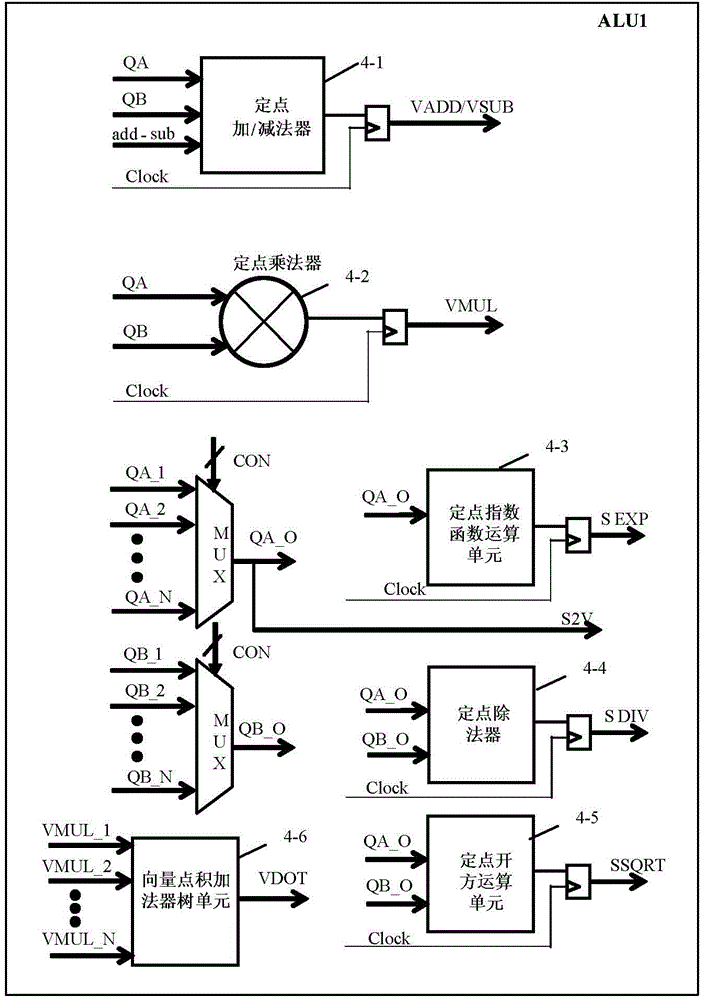

[0037] Embodiment 2. This embodiment is a further description of the fixed-point vector processor described in Embodiment 1. In this embodiment, the vector memory 3 includes a vector memory 1, a vector memory 2, ..., a vector memory N; ALU 4 includes ALU 1, ALU 2, ..., ALU N; wherein, N is an integer greater than or equal to 1 and less than or equal to 128; vector memory 1 is connected to ALU 1 and forms a data path , and the vector memory 1 and the ALU 1 have the same data bit width; the vector memory 2 is connected to the ALU 2 to form a data path, and the vector memory 2 and the ALU 2 have the same data bit width; ... ; The vector memory N is connected to the arithmetic logic unit N to form a data path, and the vector memory N and the arithmetic logic unit N have the same data bit width.

[0038] Each vector memory forms a data path with the ALU, the two are directly connected, and have the same data bit width M.

specific Embodiment approach 3

[0039] Specific Embodiment 3. This embodiment is a further description of the fixed-point vector processor described in Embodiment 1. In this embodiment, the number of data paths formed by the vector memory 3 and the ALU 4 is 1-128.

[0040] In the prior art, the number of lanes of a vector processor is currently limited to powers of 2 (16, 32, 64, 128). In this embodiment, the number of data paths of the vector processor 3 can be flexibly set according to specific calculation needs. In order to reduce the complexity of hardware design, according to the design method in this paper, vector processing with any number of data paths from 1 to 128 can be realized. device. The vector processor design is a highly portable vector processor design, which can be easily transplanted to other FPGA devices.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More