Forming method of fin field-effect transistor

A fin field effect and transistor technology, which is applied in semiconductor devices, semiconductor/solid state device manufacturing, electrical components, etc., can solve the problems of source-drain punch-through, affecting the performance of fin field effect transistors, etc., to improve quality and improve diffusion barrier role, the effect of reducing the spread

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

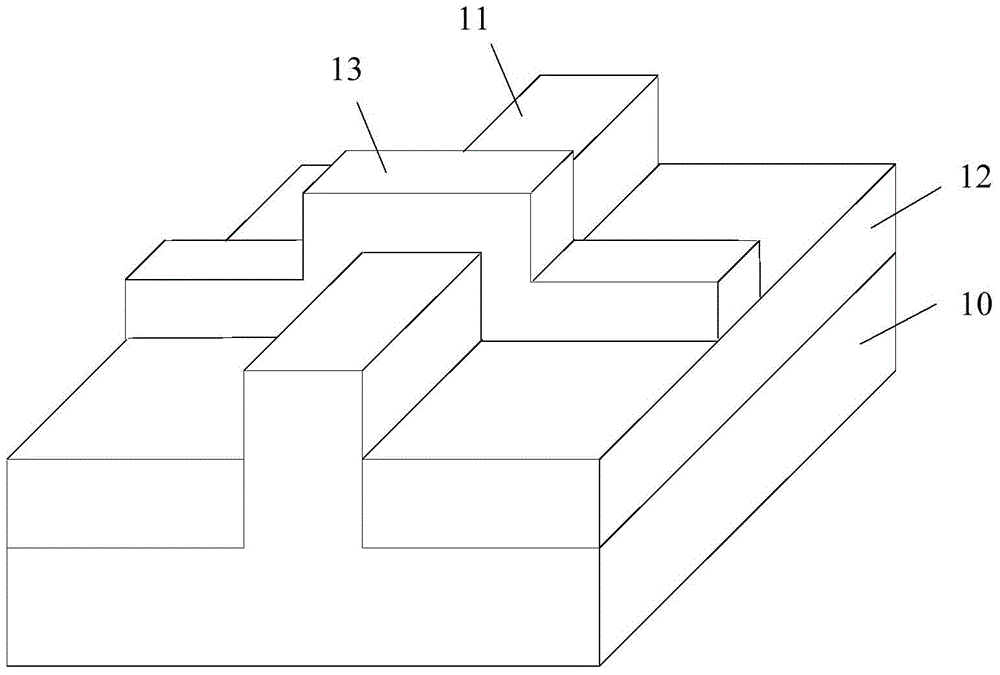

[0032] As mentioned in the background art, the fin field effect transistor formed in the prior art is prone to source-drain punchthrough phenomenon, which affects the performance of the fin field effect transistor.

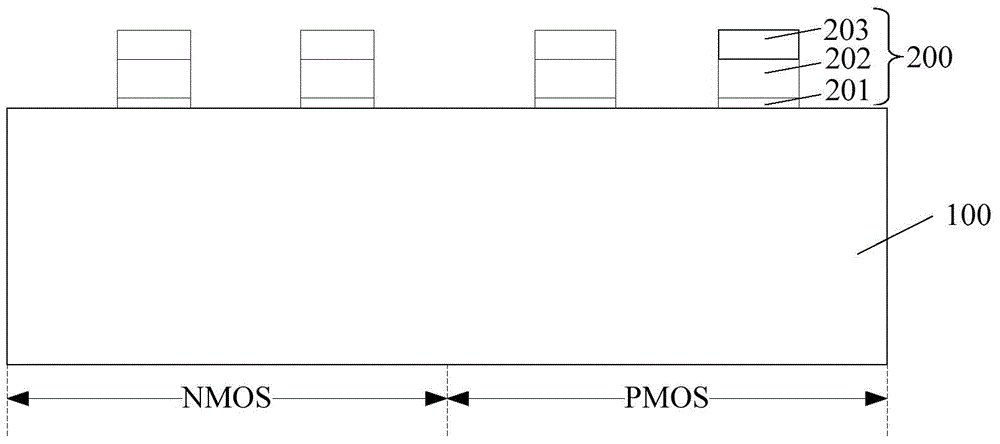

[0033] In an embodiment of forming a Fin Field Effect Transistor, after ion implantation is performed on the semiconductor substrate to form a punch-through barrier layer, the semiconductor substrate is etched to form a fin, so that the fin has a punch-through barrier layer, which can improve The punch-through voltage between source and drain.

[0034] However, studies have found that the dopant ions in the punch-through barrier layer will diffuse outward during the formation of the fin field effect transistor, and finally reduce the ion doping concentration in the punch-through barrier layer, so that the source-drain punch-through The blocking effect is reduced. This is mainly due to the fact that in the process steps after the formation of the fins, multiple he...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More