Manufacturing method of three-layer packaging substrate and three-layer packaging substrate

A technology for packaging substrates and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., and can solve the problems of expensive three-layer substrates, high warpage of three-layer packaging substrates, and asymmetric structure of three-layer substrates and other problems, to achieve the effect of reducing problems, uniform internal stress and increasing thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, but not to limit the present invention. In addition, it should be noted that, for the convenience of description, only parts related to the present invention are shown in the drawings but not all content.

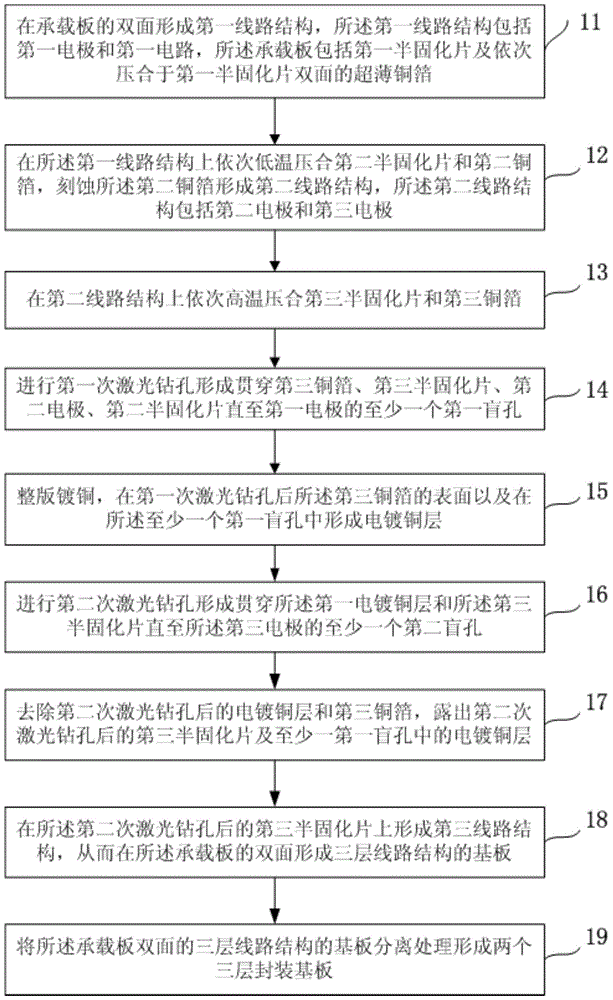

[0044] An embodiment of the present invention provides a method for manufacturing a three-layer packaging substrate. figure 1 It is a flow chart of a method for manufacturing a three-layer packaging substrate according to an embodiment of the present invention, such as figure 1 As shown, the manufacturing method of the three-layer packaging substrate includes:

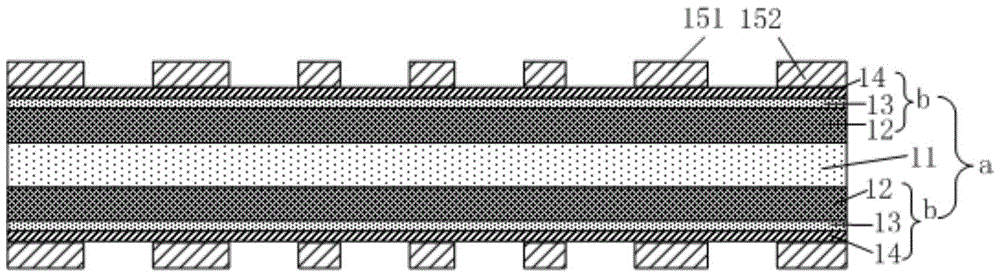

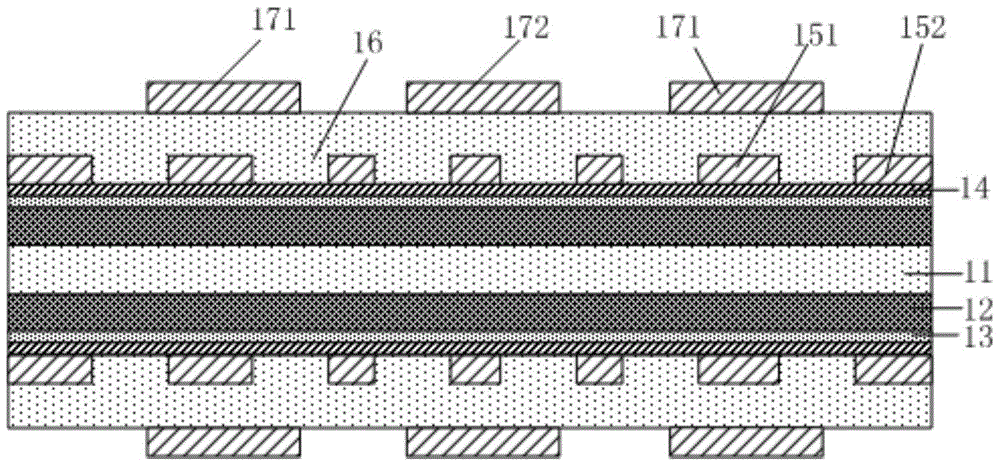

[0045] Step 11, forming a first circuit structure on both sides of the carrier board a, the first circuit structure includes a first electrode 151 and a first circuit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More