Method for polishing single silicon chip

A technology of silicon single wafer and flow tank, which is applied to surface polishing machine tools, grinding/polishing equipment, abrasives, etc., can solve problems such as waste and increase production costs, reduce flatness variation, stabilize the shape of the large disk, and improve Effect of polish removal rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

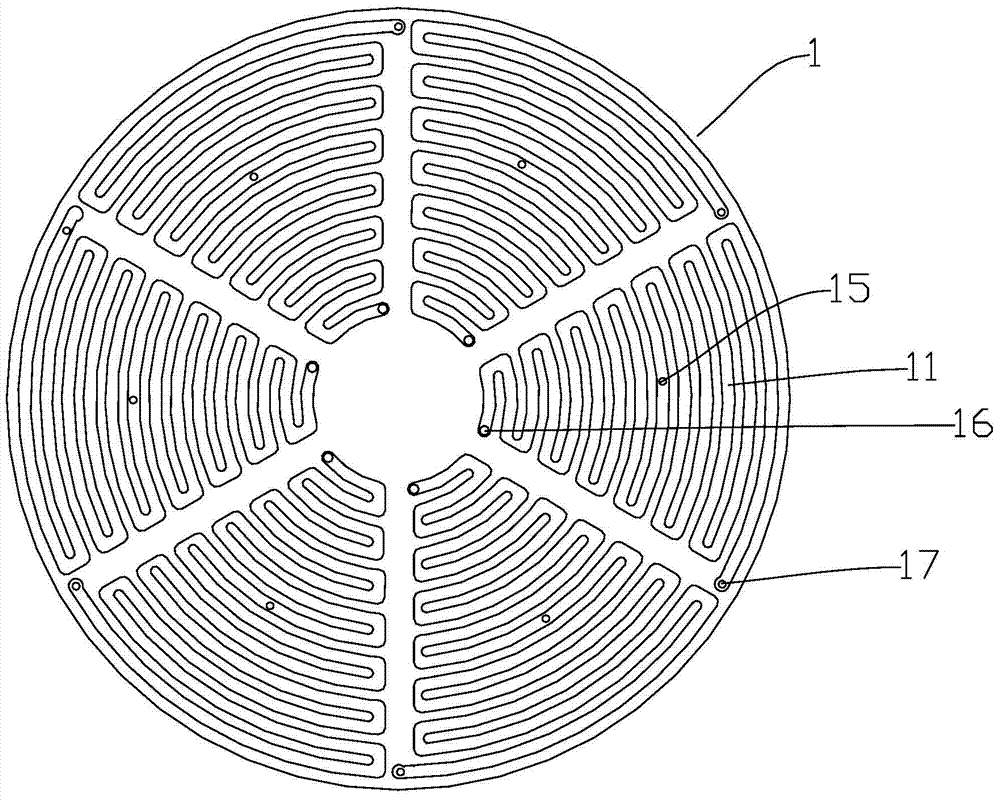

[0020] Such as figure 1 As shown in the silicon single wafer polishing method, a silicon wafer is used to polish a large plate 1 , and a flow groove 11 is arranged on the surface of the large plate 1 . The circulation groove 11 extends radially from the edge of the large disk 1 to the center of the circle and is arranged around the circumference. There are 6 circulation grooves 11 arranged along the circumferential direction. A liquid outlet 15 , a first liquid inlet 16 , and a second liquid inlet 17 are arranged in each flow tank 11 . The liquid outlet 15 is located at half the radius from the center of the circle. The first liquid inlet 16 is located near the center of the circle; the second liquid inlet 17 is located near the edge of the large plate 1 . The cooling water enters the circulation groove 11 from the liquid outlet 15 and is divided into two paths, one path flows toward the center of the circle and then enters the first liquid inlet 16 ; the other path flows t...

Embodiment 2

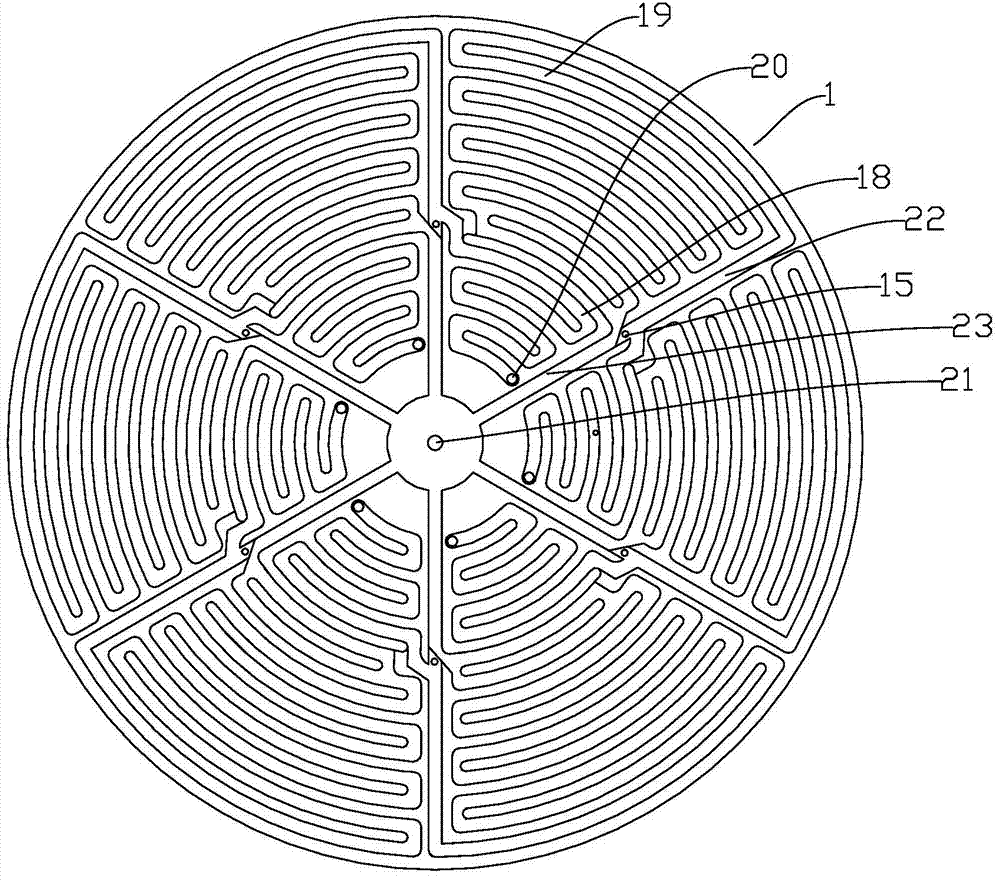

[0022] Such as figure 2 As shown, in the silicon single wafer polishing method, a silicon wafer is used to polish a large disk 1, and a flow groove is arranged on the surface of the large disk 1. The flow grooves include 6 inner ring flow grooves 18 and 6 outer ring flow grooves 19; an outer ring flow groove 19 is arranged on the periphery of an inner ring flow groove 18; a liquid outlet 15 is provided on the surface of the large plate 1; the liquid outlet 15 is located at At half the radius from the center of the circle; each liquid outlet 15 communicates with an inner ring flow groove 18 and an outer ring flow groove 19 at the same time. A third liquid inlet 20 is arranged on the surface of the large plate 1, and the third liquid inlet 20 is arranged in the inner ring flow groove 18 and is close to the center of the circle. A fourth liquid inlet 21 is provided at the center of the large plate 1 . The outer ring flow groove 19 communicates with the liquid outlet 15 through...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap