Digital calibration-based skew cancellation for long-reach mipi d-phy serial links

A serial link and serial communication technology, which is applied in the field of communication link calibration, can solve problems such as large skew, limiting the maximum data rate of link transmission, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

Detailed description of the invention

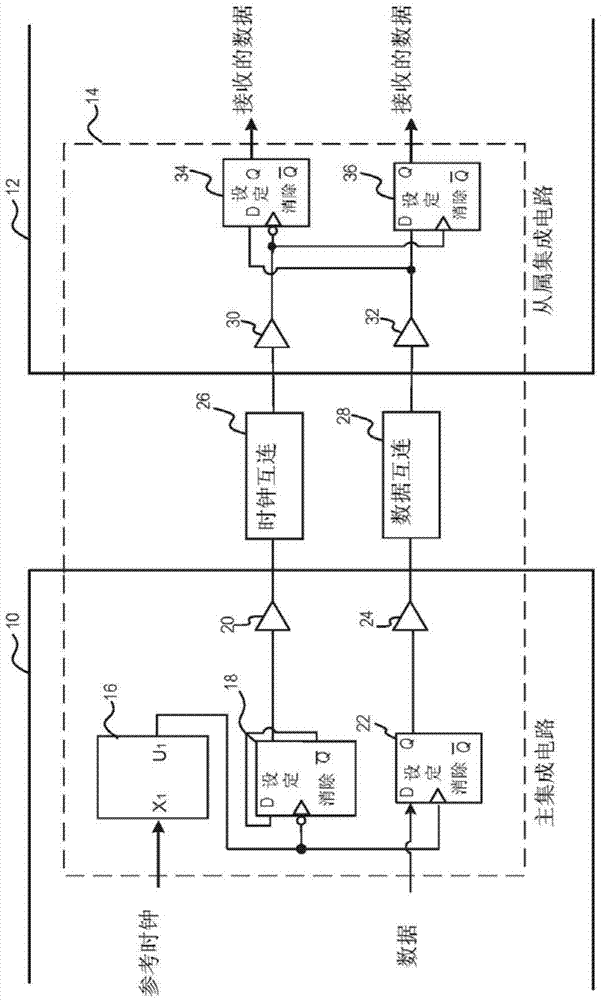

[0015] figure 1 A schematic block diagram comprising portions of two circuits, eg, integrated circuits (ICs) connected by a MIPI high-speed serial link. Please refer to figure 1 , a first integrated circuit (IC) 10, which may be referred to as a "master integrated circuit" ("Master IC"), is connected via a MIPI high-speed serial link 14 to, and may communicate with a second integrated circuit (IC) 12 for communication. Such as figure 1 As shown, a reference clock signal is input to a frequency multiplier 16 of a phase locked loop (PLL), which outputs a clock signal at a bit rate. The bit rate clock signal is applied to a pair of D flip-flops 18 and 22 which are triggered on the rising and falling edges of the bit rate clock signal, respectively. Flip-Flop 18 The output is applied to the D input of flip-flop 18 such that flip-flop 18 generates a double data rate (DDR) clock signal and outputs the DDR clock signal at its Q output. T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More