Method for testing single event effect of on-chip system

A single-event effect, system-on-chip technology, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problems of complex measurement methods, no unified test method for single-event effect testing, and complex error types, and achieve data processing. The effect of convenient, convenient and quick detection and high degree of automation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0054] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

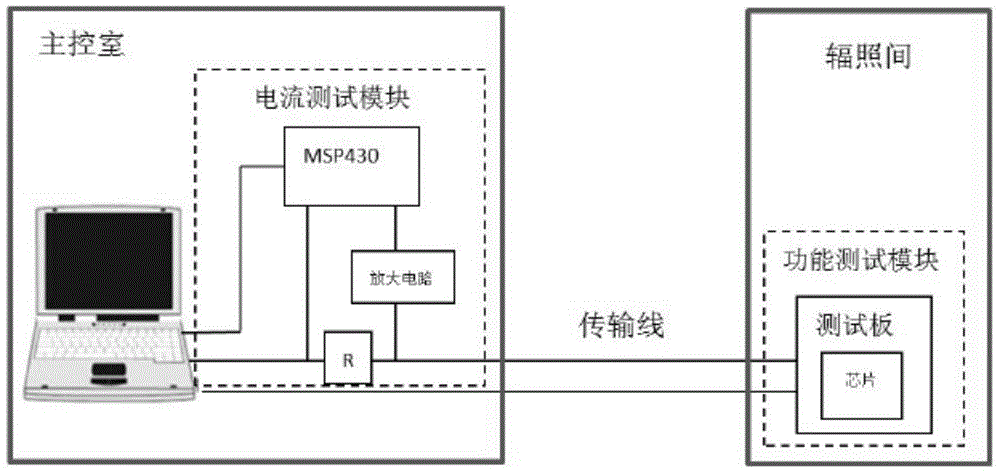

[0055] like figure 1 As shown, several components of the test method of the present invention are illustrated, including the upper computer control unit, the current test module and the lower computer SoC test board. The computer in the main control room in the figure runs the upper computer control software. The current detection unit mainly amplifies the voltage on the sampling resistor R through the amplification circuit, and then converts the voltage through the MSP430 single-chip microcomputer to obtain the working current value after conversion. The test board is located in the irradiation room, and the irradiation source is perpendicular to the SoC chip during the test.

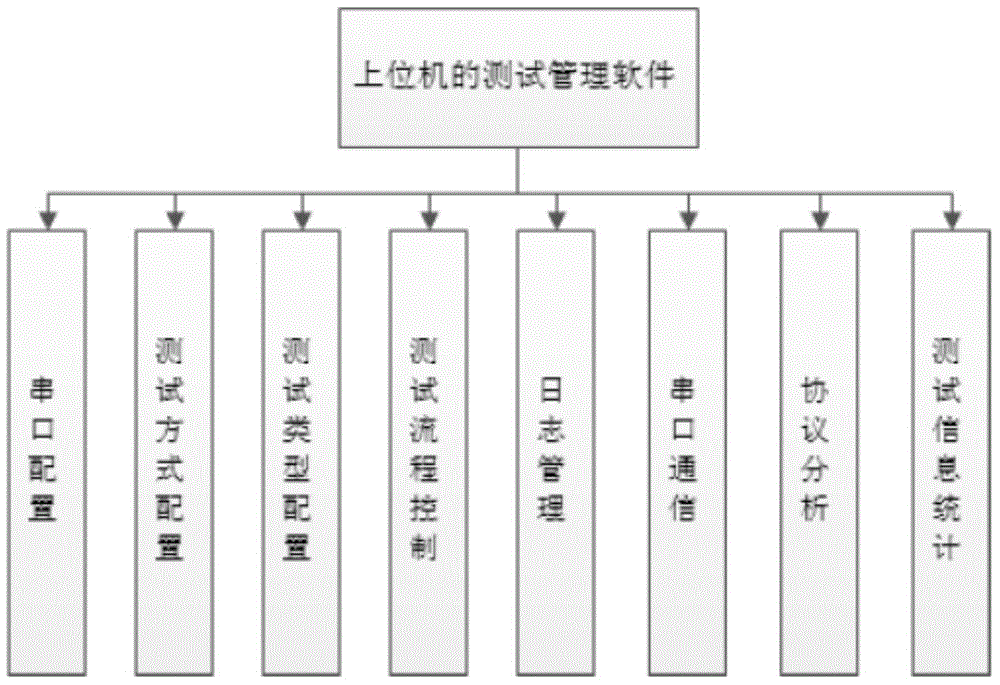

[0056] like figure 2 Shown are several main functions of the host computer management software. Including serial port configuration, test mode configuration...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More