CMOS transistor and forming method thereof

A transistor and semiconductor technology, applied in the manufacture of transistors, semiconductor devices, semiconductor/solid-state devices, etc., can solve problems such as poor performance of CMOS transistors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

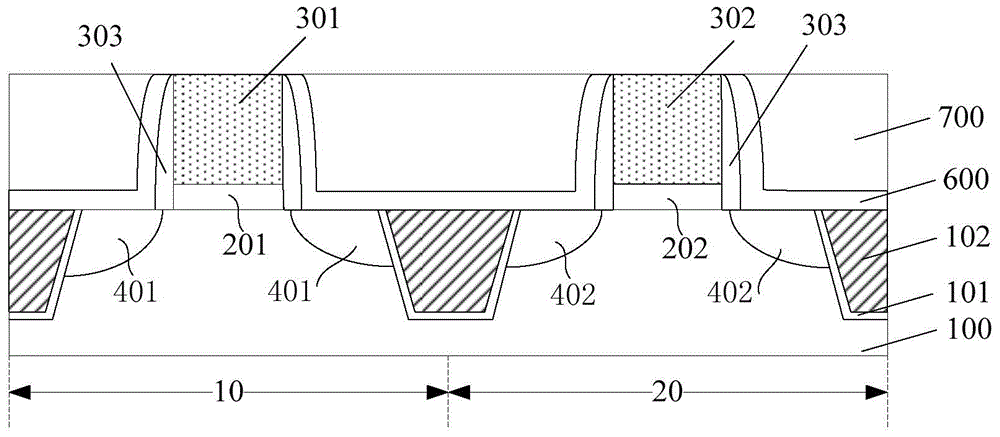

[0031] As mentioned in the background art, the performance of the CMOS transistors formed in the prior art is relatively poor and needs to be further improved.

[0032] It is found through research that the metal gate of the CMOS transistor is generally made of metal materials such as Al and Cu, and the metal atoms in the metal gate will diffuse into the work function layer, affecting the work function of the CMOS transistor; and, because The size of the CMOS transistor is small, the thickness of the work function layer is low, and the metal atoms will also diffuse into the high-K gate dielectric layer through the work function layer, affecting the dielectric constant of the high-K gate dielectric layer, and easily A gate leakage current is formed, thereby affecting the performance of the CMOS transistor. The diffusion of metal atoms can be blocked by forming a barrier layer on the surface of the gate dielectric layer, but due to the small size of the groove, only a barrier la...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More