Formation method of semiconductor structure

A semiconductor and gate structure technology, applied in the field of semiconductor structure formation, can solve the problems of increasing gate parasitic capacitance, shrinking semiconductor device size, affecting transistor performance, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

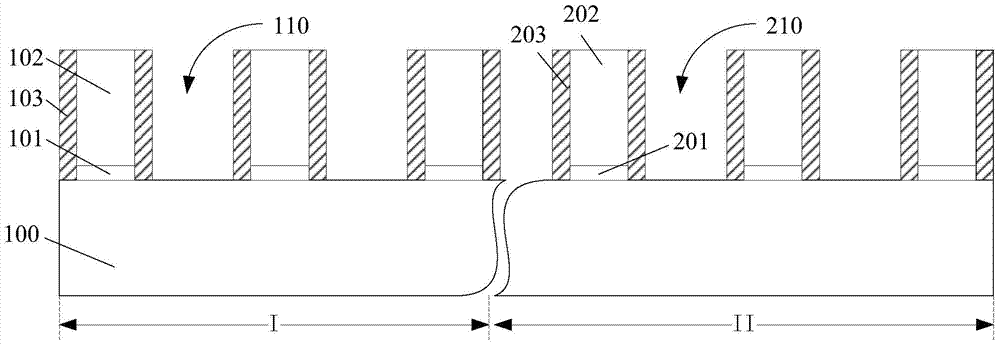

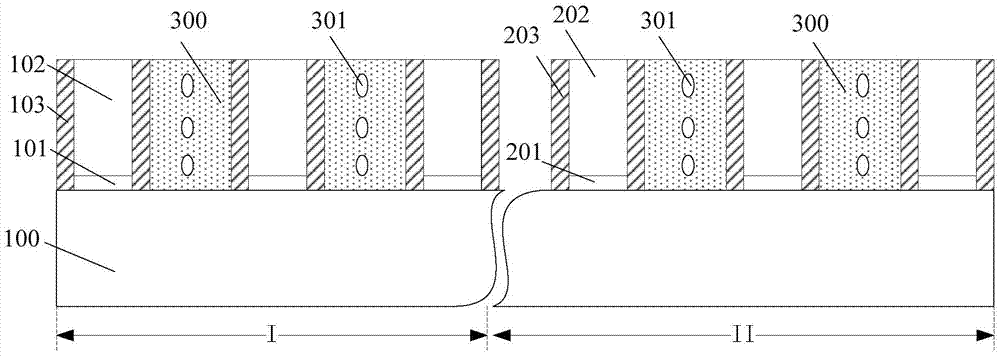

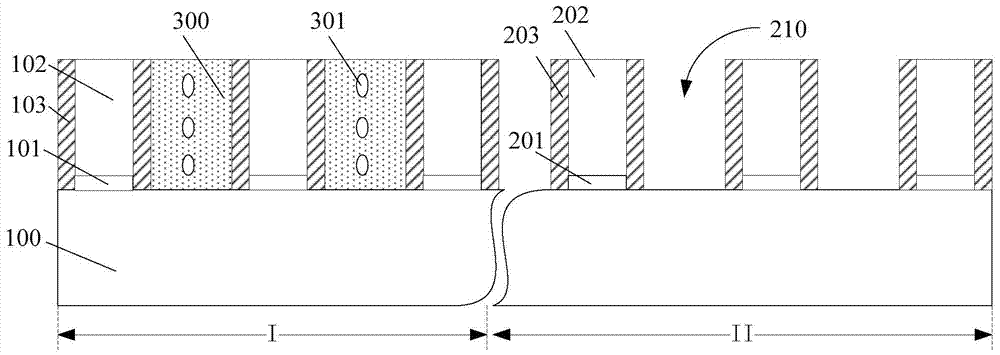

[0032] As mentioned in the background art, in existing integrated circuits, the distances between the gates of adjacent transistors and between the gates and the metal plugs are small, so large parasitic capacitances are formed.

[0033] The operating speed of devices in the core area of the integrated circuit is inversely proportional to the parasitic capacitance, and the core area may be devices such as processors and memories. The greater the parasitic capacitance, the lower the operating speed of the device. The core area is a sensitive area for parasitic capacitance, and the device in the core area generally has a low operating voltage, and the compactness of the dielectric layer between adjacent gates is not high. . However, in the peripheral area of the integrated circuit, such as the input or output transistor, the parasitic capacitance has little influence on the performance of the transistor, and the peripheral area is an insensitive area of the parasitic capac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More