Pad structure and manufacturing method thereof

A pad and metal pad technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as insufficient bonding force, impact on device performance and yield, and pad drop-off

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

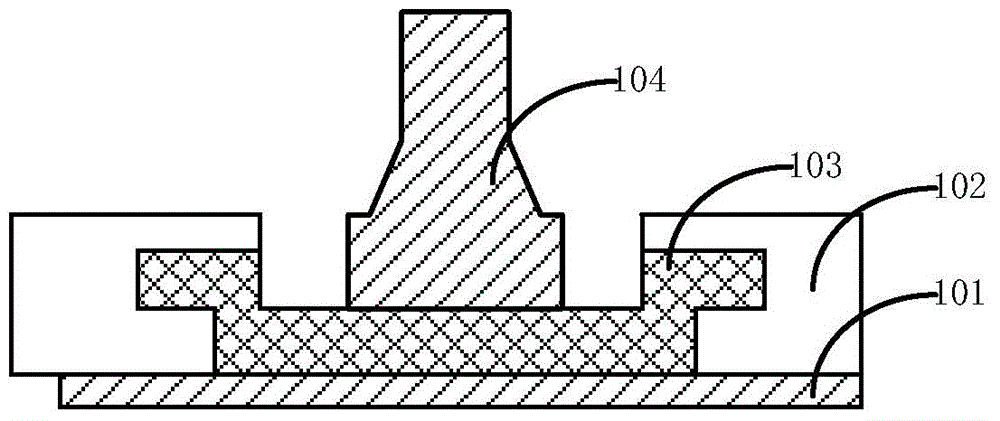

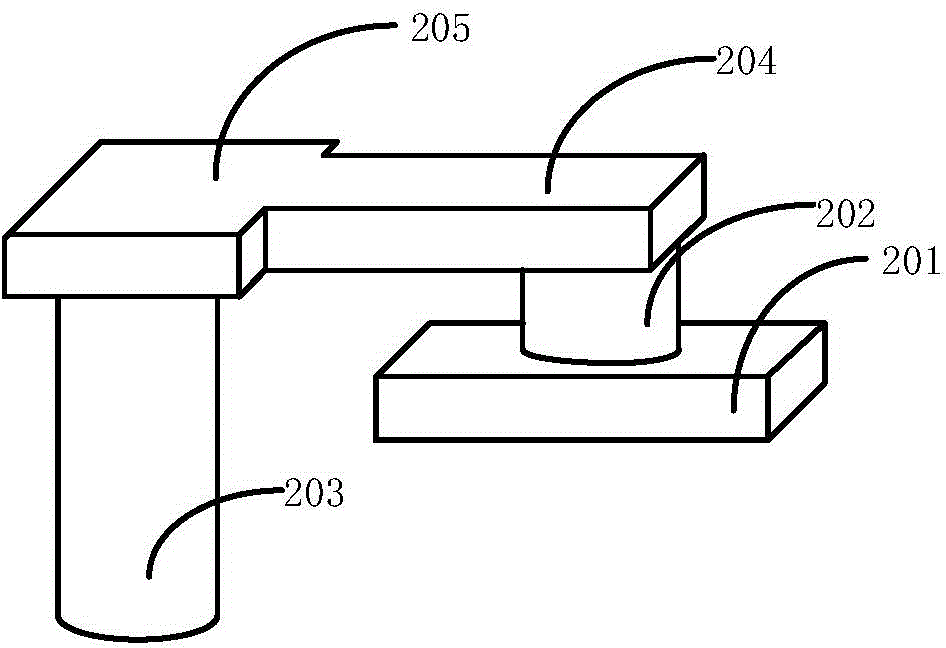

[0073] Attached below Figure 3a and 3b The pad structure described in a specific implementation manner of the present invention will be further described.

[0074] in Figure 3a It is a schematic diagram of the three-dimensional structure of the bonding pad in a specific embodiment of the present invention; Figure 3b It is a schematic cross-sectional view of the bonding pad in a specific embodiment of the present invention.

[0075] Specifically, the pad structure includes a metal pad 205, metal lines 202, 204, a top metal layer 201, a nail pad 203, and an isolation material layer.

[0076] Wherein, the metal pad 205 is an Al pad, but it is not limited to one type of Al pad, and those skilled in the art may select other commonly used metal pads.

[0077] The shape of the metal pad 205 can be square, such as Figure 3a As shown, it can be a rectangle or a square. In addition, other shapes, such as rhombus, triangle or polygon, can also be used, and other irregular patter...

Embodiment 2

[0097] The invention also provides a preparation method of the pad structure.

[0098] First, step 201 is performed to provide a base, which at least includes a semiconductor substrate (not shown in the figure), on which various active devices and interconnection structures are formed, and the semiconductor substrate may be At least one of the materials mentioned below: silicon, silicon-on-insulator (SOI), silicon-on-insulator (SSOI), silicon-germanium-on-insulator (S-SiGeOI), and silicon-germanium-on-insulator (SiGeOI), etc. . A doped region and / or an isolation structure may be formed in the substrate, and the isolation structure is a shallow trench isolation (STI) structure or a local oxide of silicon (LOCOS) isolation structure.

[0099] Step 202 is executed to form an interlayer dielectric layer 206 on the substrate.

[0100] Specifically, an interlayer dielectric layer 206 is deposited on the substrate, and the interlayer dielectric layer 206 may be a metal interlayer d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More