Formation method of CMOS transistor

A transistor and gas technology, applied in the field of CMOS transistor formation, can solve the problems of metal gate quality degradation, sidewall concave, CMOS transistor performance degradation, etc., to achieve the effects of flat sidewall surface, improved performance, and prevention of accumulation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

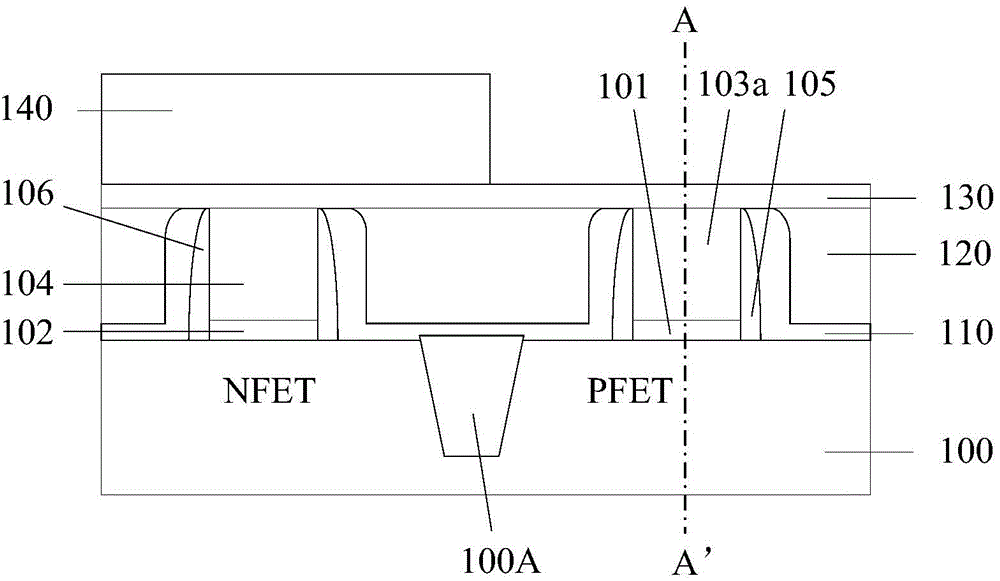

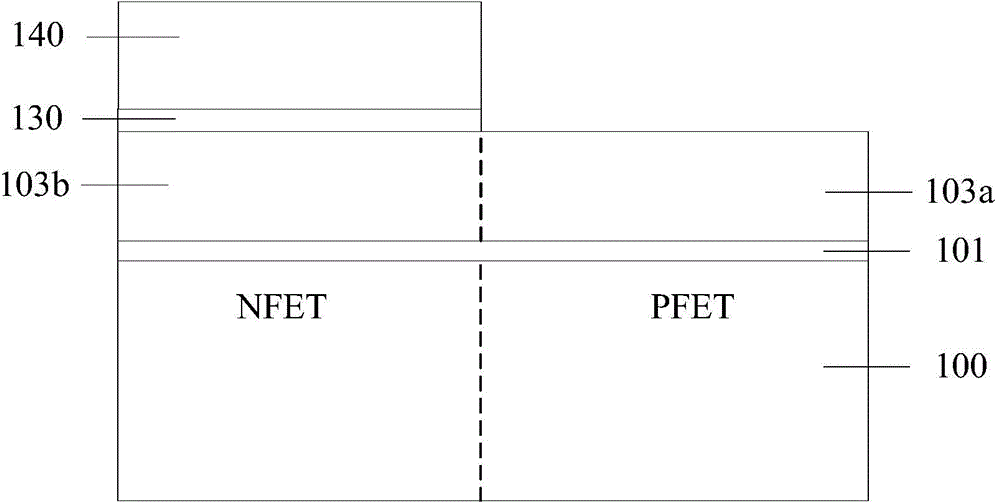

[0038] In a CMOS transistor using a high-K dielectric layer-metal gate (HKMG), the work function metal materials used in the NMOS transistor and the PMOS transistor that make up the CMOS transistor are usually different, so the dummy gates of the NMOS transistor and the PMOS transistor need to be removed separately . However, as described in the background art, when the first dummy gate and the second dummy gate connected together are etched in the existing CMOS transistor formation method, after the first dummy gate is removed, the second dummy gate is prone to appear The sidewall concave problem causes the performance of the finally formed CMOS transistor to degrade.

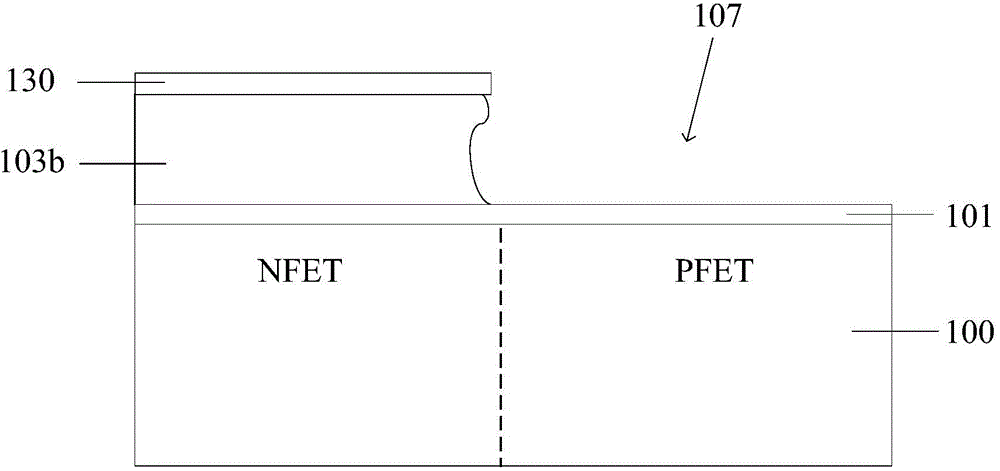

[0039] To this end, the present invention provides a new method for forming a CMOS transistor, which uses a first pulse plasma etching process to remove part of the thickness when etching the first dummy gate and the second dummy gate that are connected together. the first dummy gate, and expose part of the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More