Silicon through hole test circuit and method thereof, test circuit of silicon through hole group in three-dimensional integrated circuit and method thereof

A technology for testing circuits and through-silicon vias, which is applied in the direction of circuits, semiconductor/solid-state device testing/measurement, electrical components, etc. It can solve problems such as TSV open circuit, void, crack, and TSV resistance increase, and achieve the goal of improving yield Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

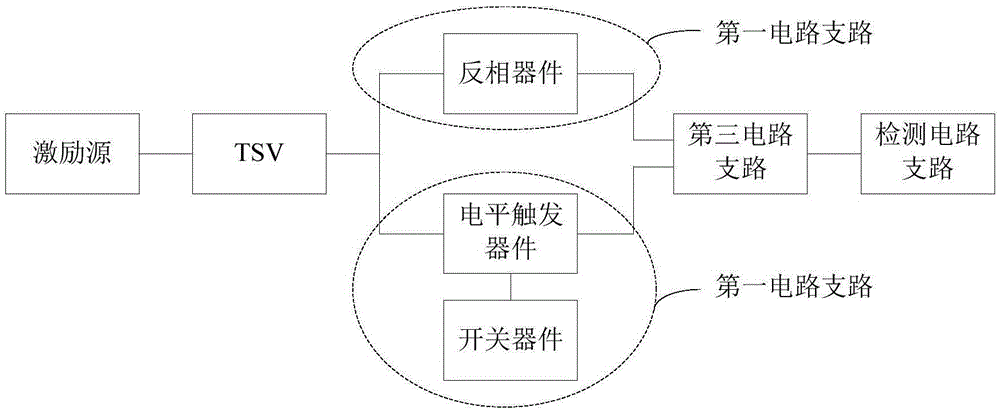

[0041] Due to the characteristics of the three-dimensional integrated circuit process, the TSV test needs to be divided into two stages: pre-bond and post-bond. In the pre-bond test stage, TSVs are usually in the form of blind holes, and TSVs can usually be contacted by test probes, and some testability design schemes can also be used to assist. In the post-bond stage, the interlayer stacking interconnection of chips has been completed, and TSVs have been buried in the stack to play the role of interlayer interconnection. At this point, probe contact of the TSV becomes very difficult or even impossible.

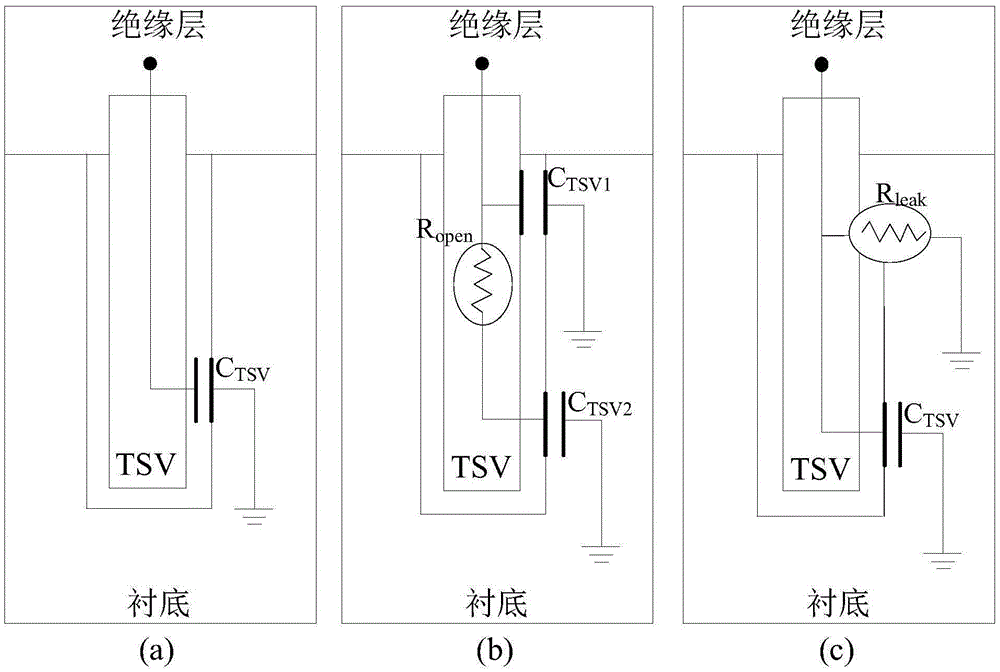

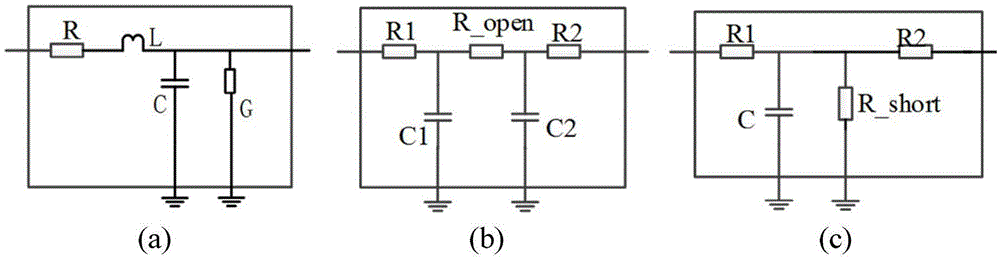

[0042] Such as figure 2 , where (a), (b), and (c) show schematic diagrams of the circuit model of TSV and its open and short defects, respectively.

[0043] Such as figure 2 As shown in (b), during the open defect test, a pulse signal is input to the TSV. Since the parasitic RC parameters in the TSV are very small, the rise and fall times of the signal passing through t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More