Chemical palladium plating method for back through hole metallization seed layer of semiconductor

A semiconductor and electroless plating technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as high process cost, uneven metal layer thickness, faults, etc., achieve broad market prospects, wide application range, Good quality workmanship

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

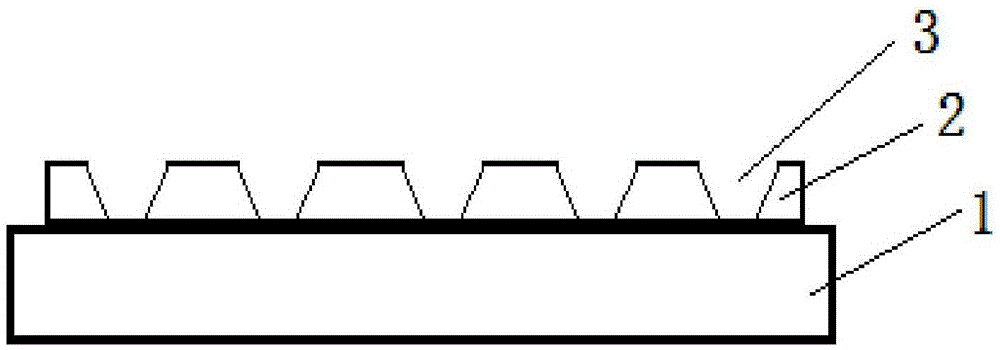

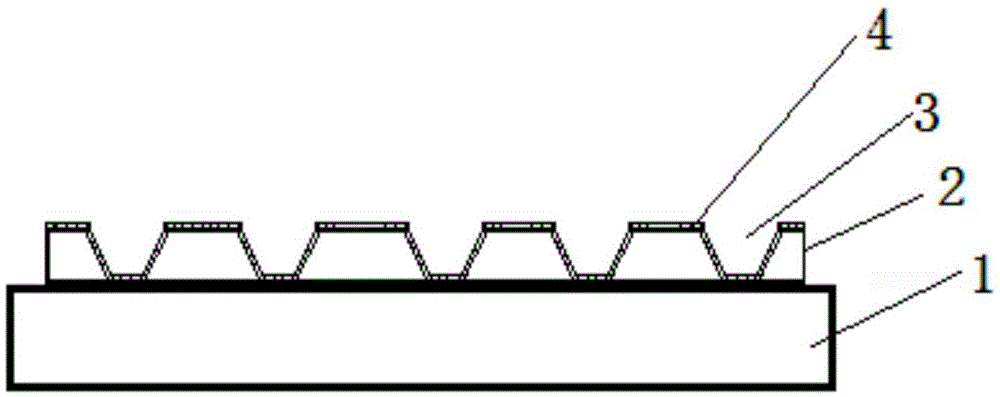

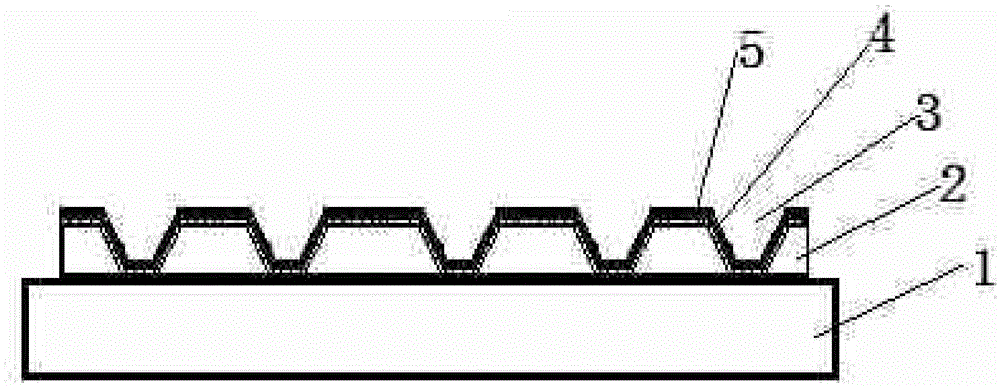

[0029] The present invention proposes an electroless palladium plating method for the through-hole metallization seed layer on the back of the semiconductor, through which palladium ions and reducing agents in a strong acid environment undergo a strong oxidation-reduction reaction with the semiconductor material and the metal surface to replace the palladium on the semiconductor material and the metal surface A layer of palladium seed crystals, and then continuously deposit palladium metal on the palladium seed crystals through the self-excitation of the plating solution in the palladium electroless plating solution, so as to obtain a certain thickness of palladium metal layer on the surface of semiconductor materials and metals to form backside through hole metallization The seed layer is then electroplated on the back of the semiconductor chip that has been electroless palladium plated, and the metallization of the back through hole is completed by using the metal at the botto...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More