Metal oxide thin film transistor with top gate structure and manufacturing method thereof

A technology of oxide thin film and oxide semiconductor, which is applied in transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of complex overall process and increased production cost, and achieve excellent device performance, low cost, and simple manufacturing process Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

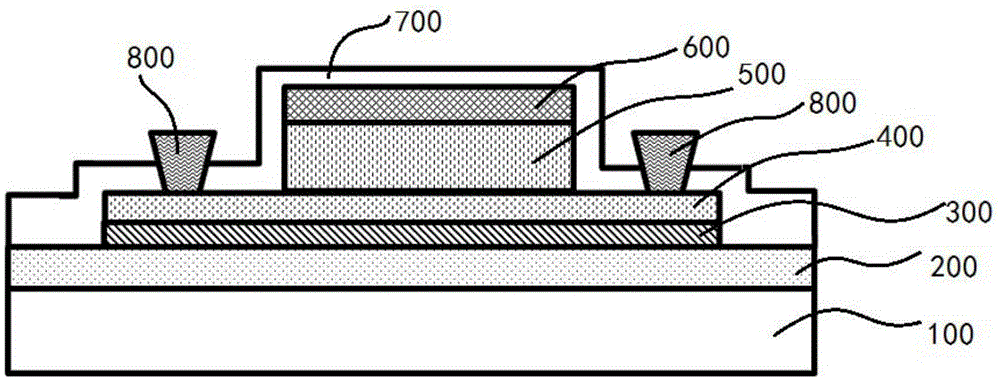

[0036] A metal oxide thin film transistor with a top gate structure, its structure is as follows figure 1 shown. Its preparation method comprises the following steps:

[0037] a. preparing a buffer layer 200 on the substrate 100;

[0038] b. Continuously deposit an opaque insulating light-shielding layer 300 and a metal oxide semiconductor layer on the buffer layer 200, and then pattern the prepared metal oxide semiconductor layer as the active layer 400, while using the patterned metal oxide The semiconductor layer, that is, the active layer 400 is used as a self-aligned pattern to pattern the light-shielding layer 300;

[0039] c. Continuously depositing the first insulating layer and the first metal layer on the active layer 400, then patterning the first metal layer as the gate electrode 600, and then using the patterned gate electrode 600, using a self-alignment method, patterning the first insulating layer as the gate insulating layer 500;

[0040] d. Depositing and ...

Embodiment 2

[0051] A method for preparing a metal oxide thin film transistor with a top gate structure is carried out through the following steps:

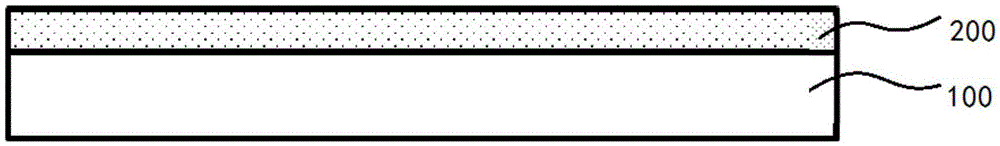

[0052] a. Deposit 300nm SiO on substrate 100 using PECVD 2 As a buffer layer 200, such as figure 2 shown.

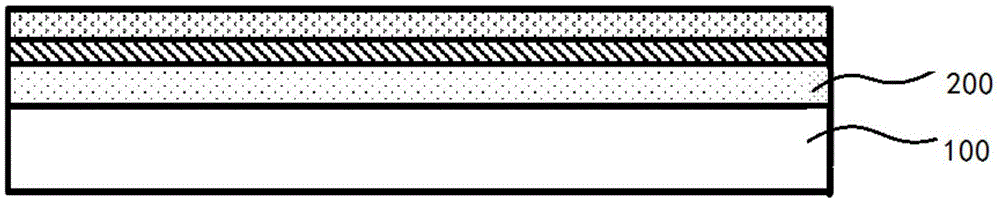

[0053] b. on the buffer layer 200, use the PVD method to continuously deposit the C film of 100nm and the IGZO film of 50nm, such as image 3 shown. Then use HCl with H 2 O ratio is 1:60 dilute hydrochloric acid patterning IGZO thin film obtains active layer 400, then uses N 2 The O gas plasma treatment method uses the active layer 400 as a mask to pattern the C film light-shielding layer 300, such as Figure 4 shown.

[0054] c. Using PECVD method to sequentially deposit 300nm SiO 2 The first insulating layer and the 200nm thick Mo layer are used as the first metal layer, and then the first metal layer is patterned as the gate electrode 600, and then the first insulating layer is patterned by using the self-alignment method wit...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More