Power-on reset circuit

A technology of electric reset and circuit, applied in the direction of electrical components, electronic switches, pulse technology, etc., can solve problems such as influence, achieve the effect of reducing discreteness and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

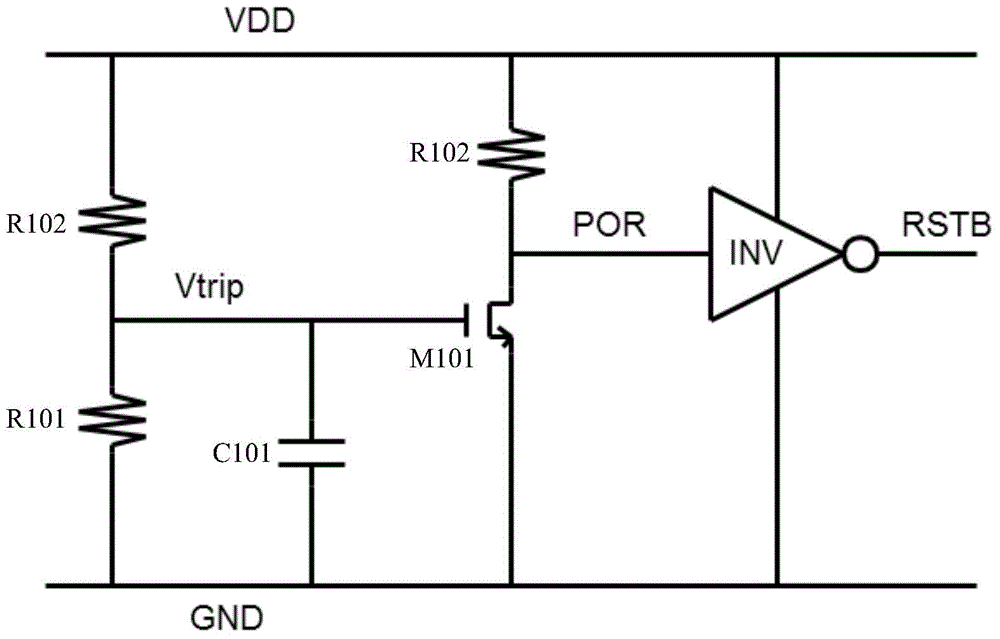

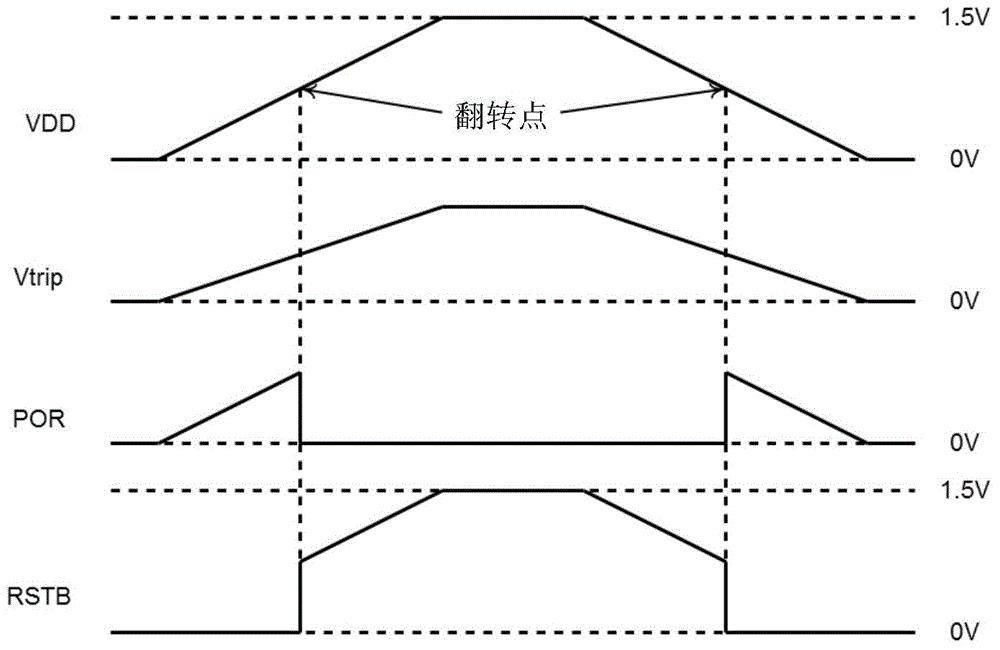

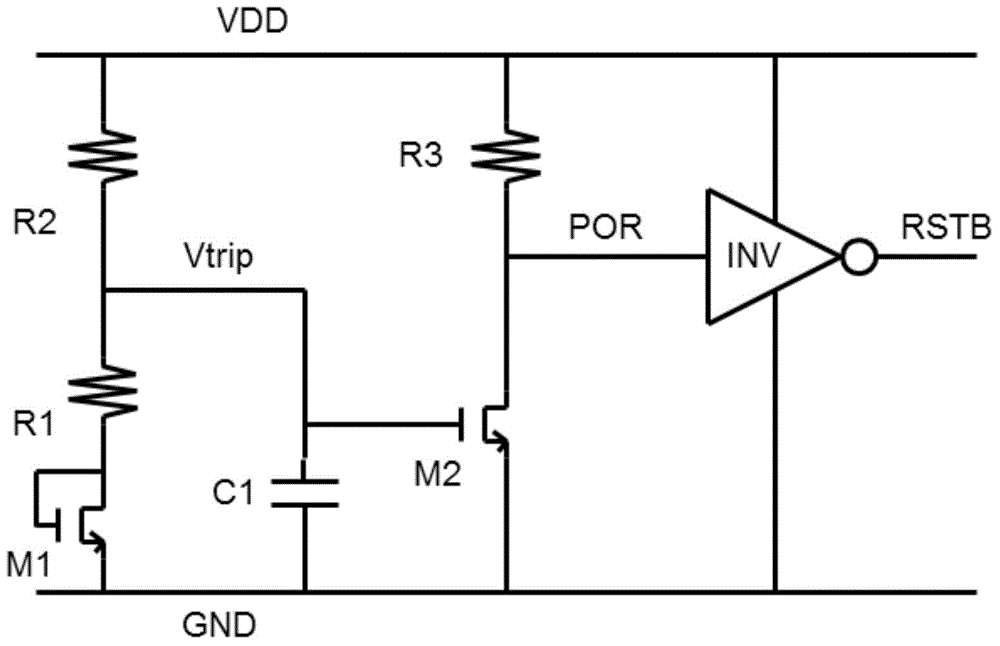

[0027] Such as image 3 Shown is the circuit diagram of the power-on reset of the embodiment of the present invention; the power-on reset circuit of the embodiment of the present invention includes:

[0028] A first voltage divider circuit connected between the power supply voltage VDD and ground GND, the first voltage divider circuit is formed by a plurality of resistors connected in series with a first NMOS transistor M1, the output terminal of the first voltage divider circuit outputs the The voltage division of the power supply voltage VDD is used as the flipping voltage Vtrip, and the gate and drain of the first NMOS transistor M1 are short-circuited and connected in series between the output terminal of the first voltage dividing circuit and the ground GND.

[0029] Preferably, the resistor string of the first voltage divider circuit includes a first resistor R1 and a second resistor R2, and the second resistor R2 is connected between the power supply voltage VDD and the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More