FPGA wiring method and device

A wiring method and wiring device technology, applied in CAD circuit design, special data processing applications, instruments, etc., can solve problems such as insufficient FPGA wiring scheme

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

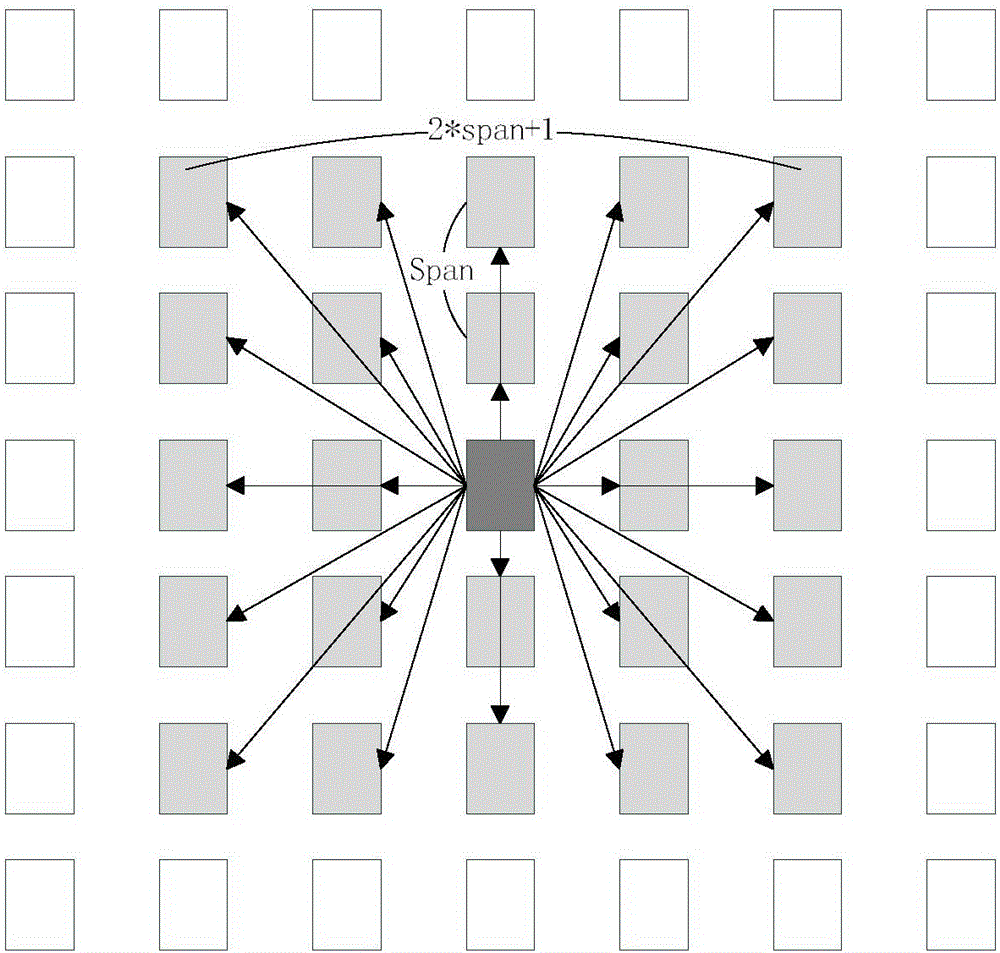

[0037] In the present invention, the cost may be a single factor such as delay, path, conflict, or a combination of multiple factors. The cost estimation model can be in the form of a list, and the router loads the list when starting the routing, parses it and stores it in the hash table, that is, realizes the cost value estimation between nodes based on the look-up table.

[0038] The concept of the present invention will be further described in detail through specific embodiments below.

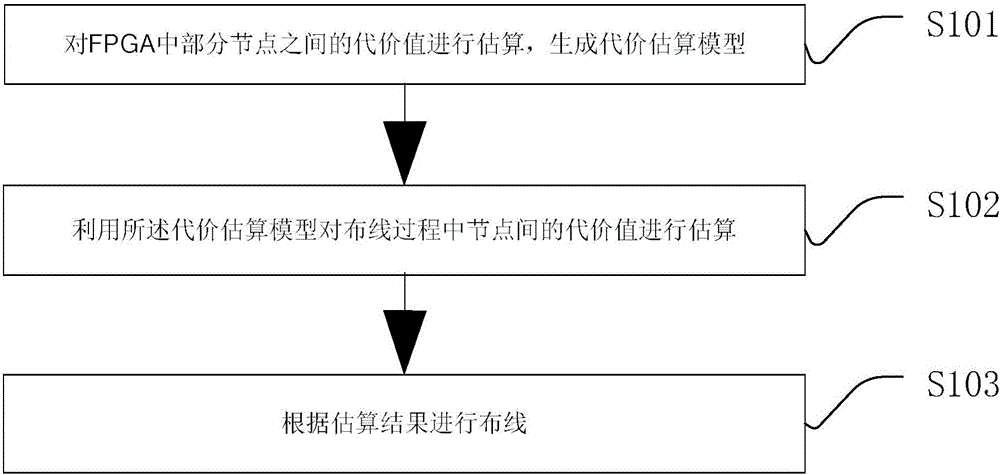

[0039] Such as figure 2 As shown, the flow chart of the FPGA wiring method provided by an embodiment of the present invention mainly includes the following steps:

[0040] S101. Estimate the cost value between some nodes in the FPGA, and generate a cost estimation model;

[0041] S102. Using the cost estimation model to estimate the cost value between nodes in the wiring process;

[0042] S103. Perform wiring according to the estimation result.

[0043] Step S101 includes but is not li...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More