Method for optimizing FPGA (Field-Programmable Gate Array) chip layout based on area clock

A regional clock and chip layout technology, applied in the direction of logic circuits using basic logic circuit components, logic circuits using specific components, etc., can solve problems such as setup time violations, hold time violations, timing violations, etc., to achieve FPGA layout optimization, Effect of reducing wiring length and improving layout

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] In order to make the purpose, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings. Obviously, the described embodiments are only some of the embodiments of the present invention, rather than all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

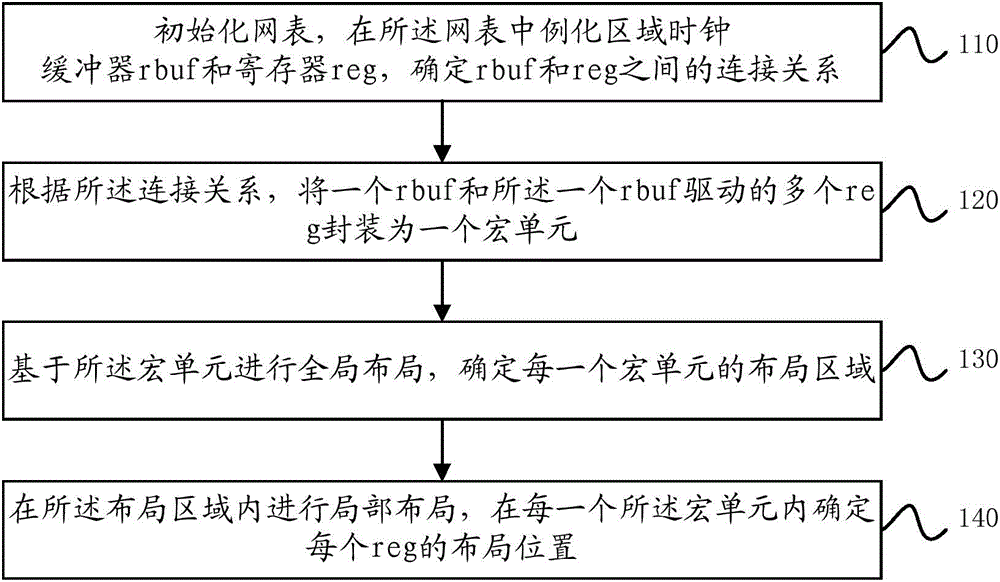

[0026] figure 1 An embodiment of the present invention provides a flow chart of a method for optimizing a local layout of an FPGA chip. As shown in the figure, the method includes the following steps:

[0027] Step 110, initialize the netlist, instantiate the regional clock buffer (rbuf) and register (reg) in the netlist, determine the connection relationship between rbuf and reg;

[0028] Specifically, in electronic circuit design, a netli...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More