Formation method of semiconductor structure

A semiconductor and layer-forming technology, used in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., and can solve the problem of high failure rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

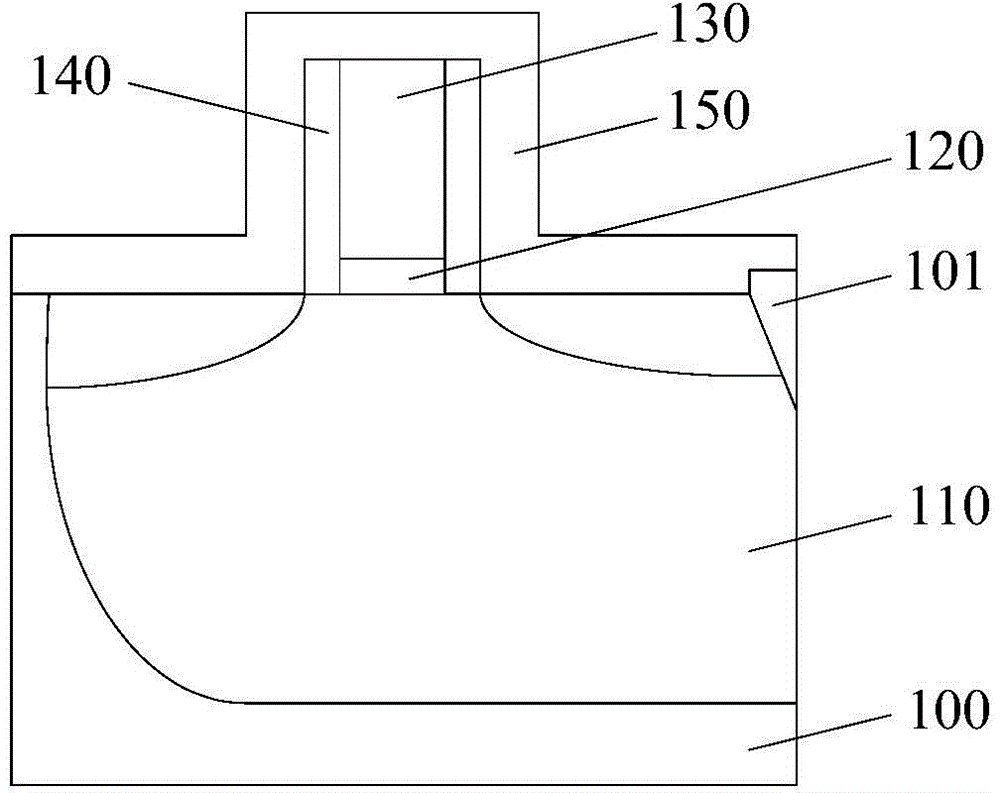

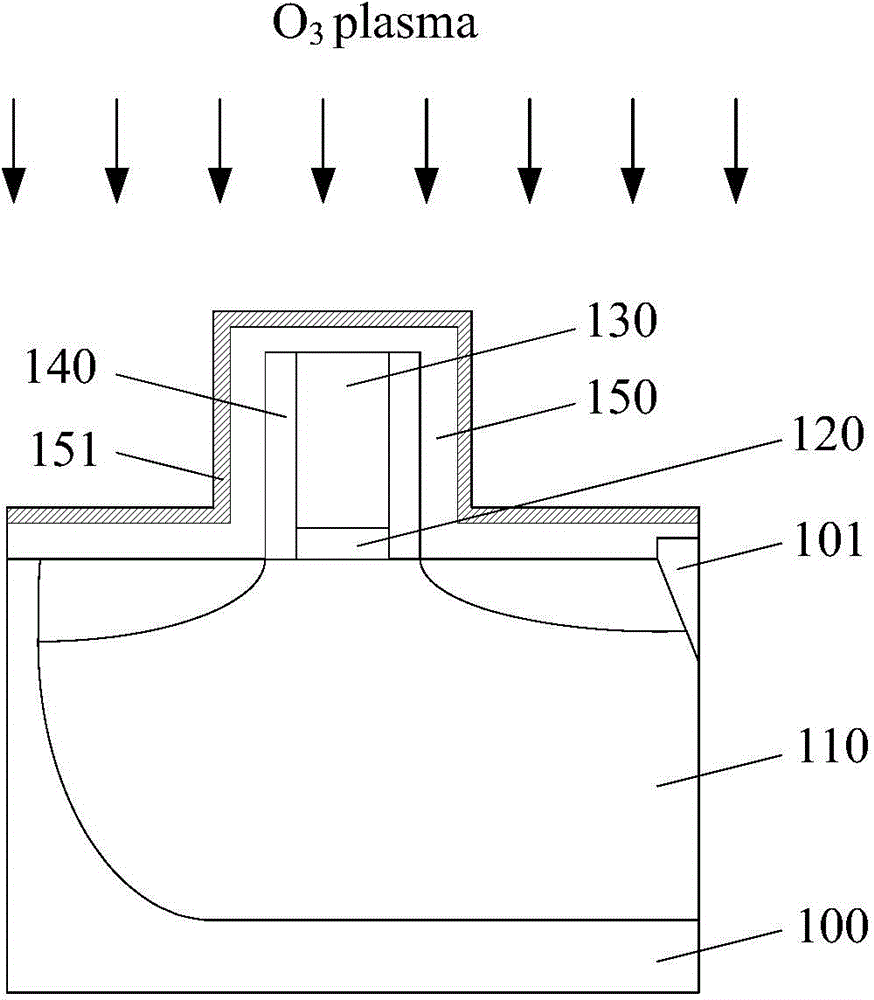

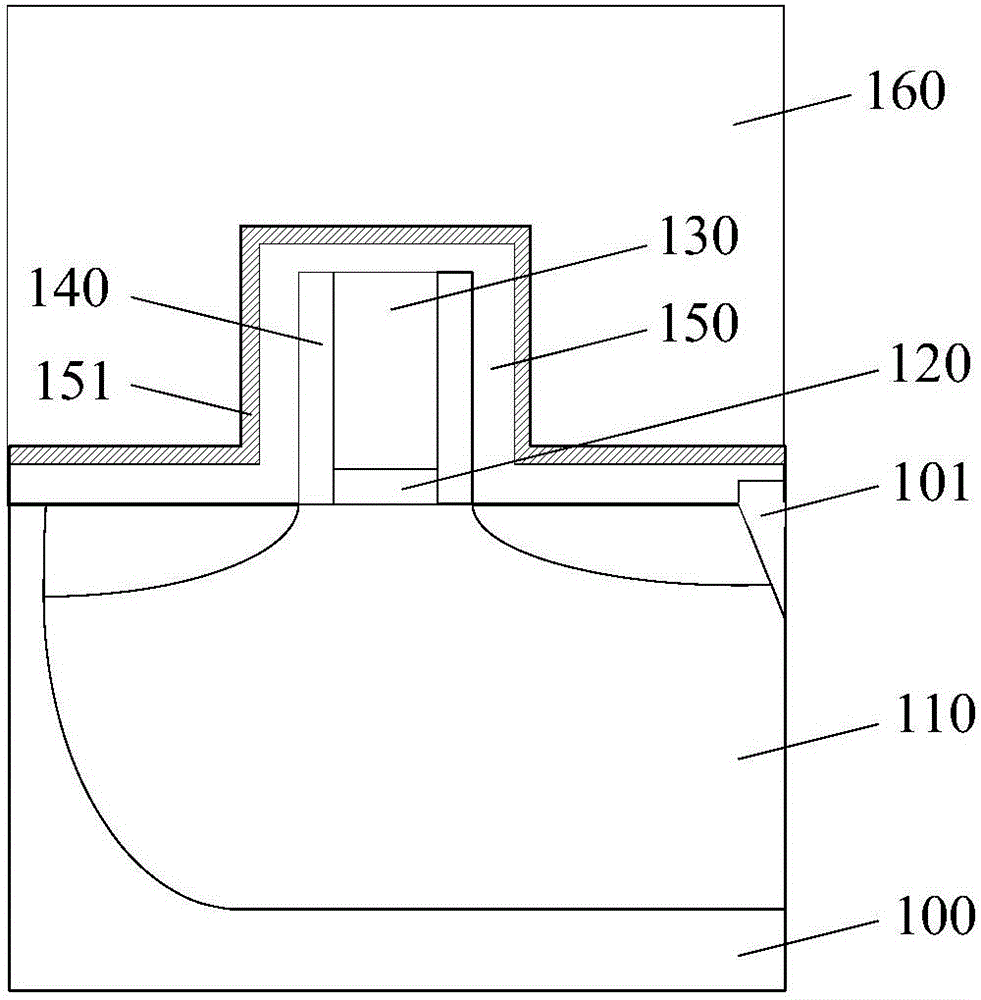

[0024] As mentioned in the background technology, after the existing method uses a high aspect ratio process to form the upper stress layer interlayer dielectric layer, when performing fault detection, the failure rate is too high. This problem is manifested in the detection of particulate matter problems. particularly serious.

[0025] Analyzing the reason, the structure of the interlayer dielectric layer formed by the high aspect ratio process is relatively soft, and the surface roughness is relatively large, which leads to the situation that the rough surface is mistakenly detected as particles in the detection of particle problems, resulting in a failure rate during fault detection. Excessively bothered.

[0026] Further analysis of the reason for the large surface roughness of the interlayer dielectric layer found that the formation material of the interlayer dielectric layer is usually tetraethyl silicate. When the high aspect ratio process directly forms the interlayer ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More