How to make a flat vdmos

A manufacturing method and planar technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of high manufacturing cost and long manufacturing cycle, and achieve the goal of reducing manufacturing cost, heat treatment process, and shortening the manufacturing cycle Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

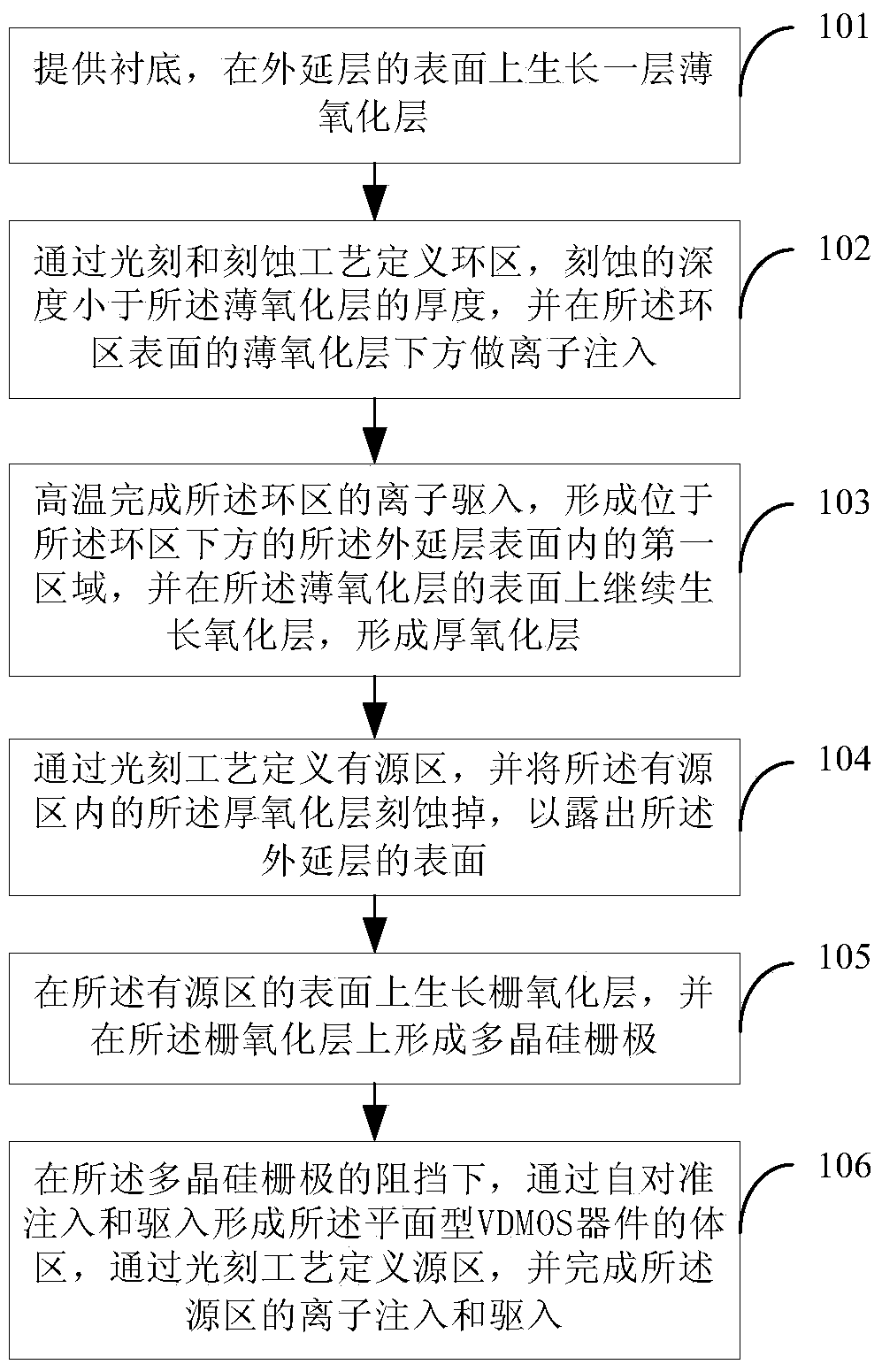

[0032] figure 1 A schematic flow chart of the planar VDMOS manufacturing method provided in Embodiment 1 of the present invention, as shown in figure 1 As shown, the planar VDMOS manufacturing method provided in this embodiment includes the following steps:

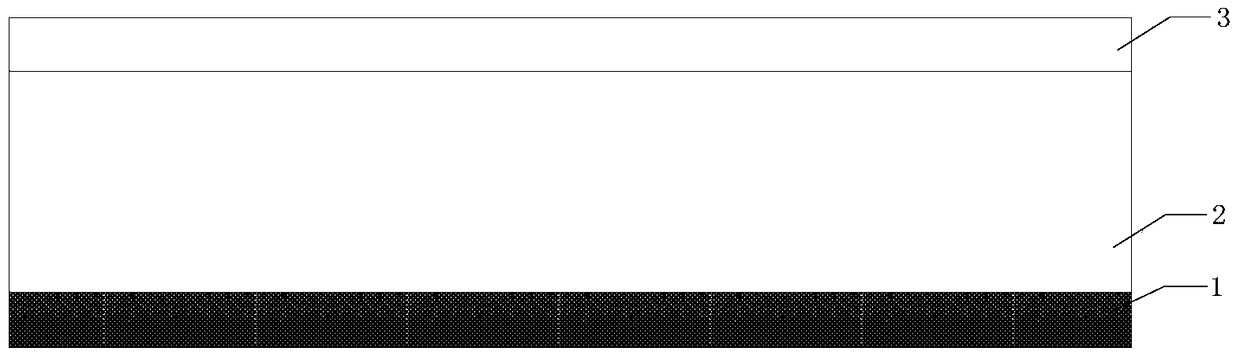

[0033] Step 101, providing a substrate, and growing a thin oxide layer on the surface of the epitaxial layer;

[0034] specific, figure 2 It is a schematic structural diagram of the planar VDMOS after performing step 101, as figure 2 As shown, preferably, the substrate provided in this embodiment includes an N-type substrate 1 and an N-type epitaxial layer 2 . The substrate is thermally oxidized for 30-60 minutes at a temperature of 900-1100 degrees to form a thin oxide layer 3 with a thickness of 1000-2000 angstroms.

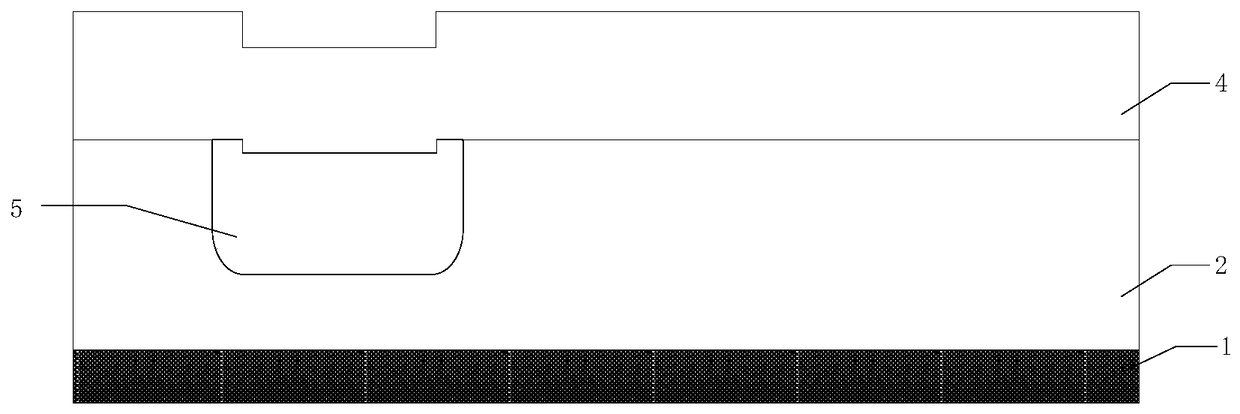

[0035] Step 102, define the ring area by photolithography and etching process, the etching depth is less than the thickness of the thin oxide layer, and perform ion implantation under the thin oxide ...

Embodiment 2

[0049] Figure 7 A schematic flow chart of the planar VDMOS fabrication method provided in Embodiment 2 of the present invention, as shown in Figure 7 As shown, the planar VDMOS manufacturing method provided in this embodiment includes:

[0050] Step 201, providing a substrate, and growing a thin oxide layer on the surface of the epitaxial layer;

[0051] Step 202, define the ring area by photolithography and etching process, the etching depth is less than the thickness of the thin oxide layer, and perform ion implantation under the thin oxide layer on the surface of the ring area;

[0052] Step 203, complete the ion drive into the ring region at high temperature to form a first region on the surface of the epitaxial layer below the ring region, and continue to grow an oxide layer on the surface of the thin oxide layer to form a thick oxide layer;

[0053] Step 204, define an active region by a photolithography process, and etch away the thick oxide layer in the active reg...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More