Neuromorphic chip simulator

A neuromorphic and simulator technology, applied in the field of neuromorphic chip simulators, can solve problems such as unsatisfactory, unavailable, and precision differences, and achieve the effect of ensuring quality and efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] Embodiments of the present invention are described in detail below, examples of which are shown in the drawings, wherein the same or similar reference numerals designate the same or similar elements or elements having the same or similar functions throughout. The embodiments described below by referring to the figures are exemplary only for explaining the present invention and should not be construed as limiting the present invention.

[0041] A simulator of a neuromorphic chip according to an embodiment of the present invention will be described below with reference to the accompanying drawings.

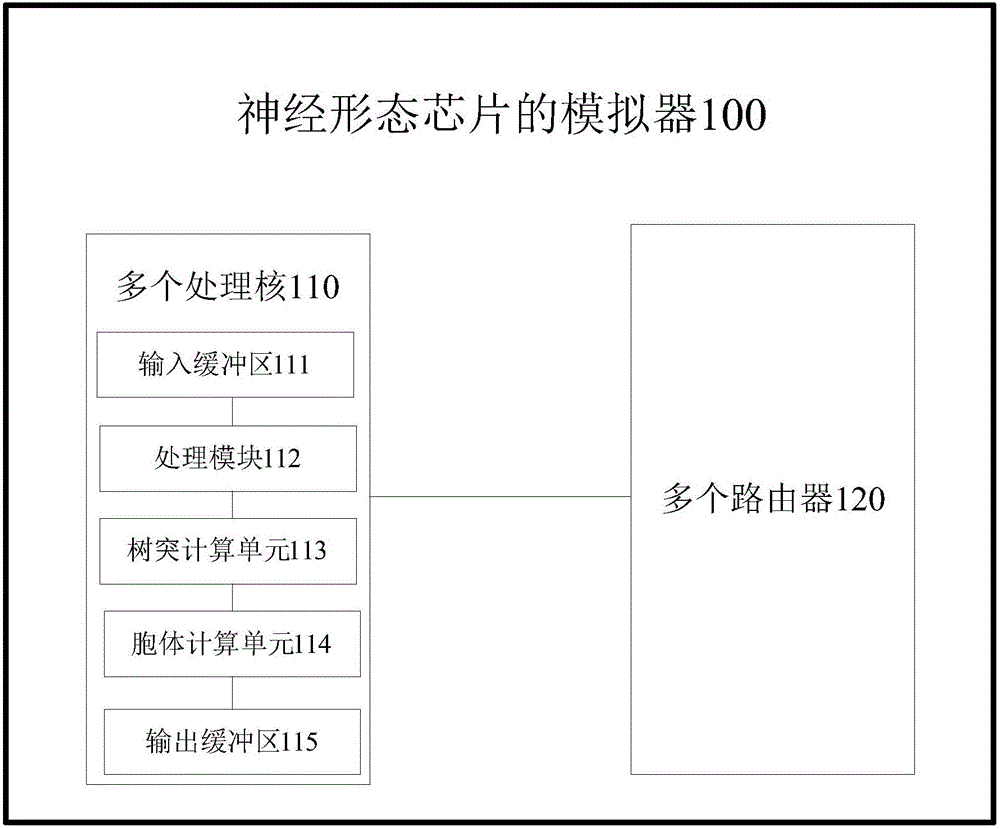

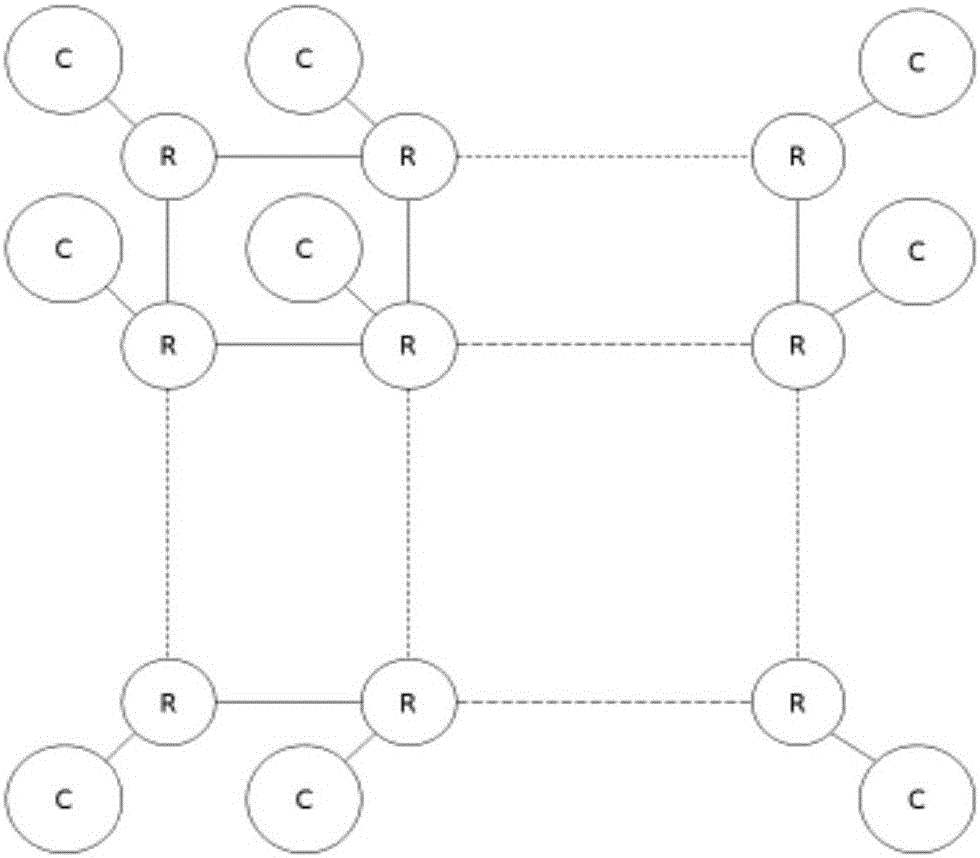

[0042] figure 1 is a system block diagram of a simulator of a neuromorphic chip according to an embodiment of the present invention. figure 2 is a schematic structural diagram of a neuromorphic chip simulator according to an embodiment of the present invention. Such as figure 1 shown, combined with figure 2 , the neuromorphic chip simulator 100 includes: multiple proces...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More