Low-power-consumption scanning testing method and device based on parallel applying of test excitation

A technology of test excitation and scan test, which is applied in the direction of measuring devices, electronic circuit testing, and measuring electronics, can solve the problems of large dynamic power consumption of combinational logic, large shift power consumption of scanning units, and large power consumption of clock trees, etc., to achieve Effects of reduced power consumption, reduced dynamic power consumption, and reduced peak power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

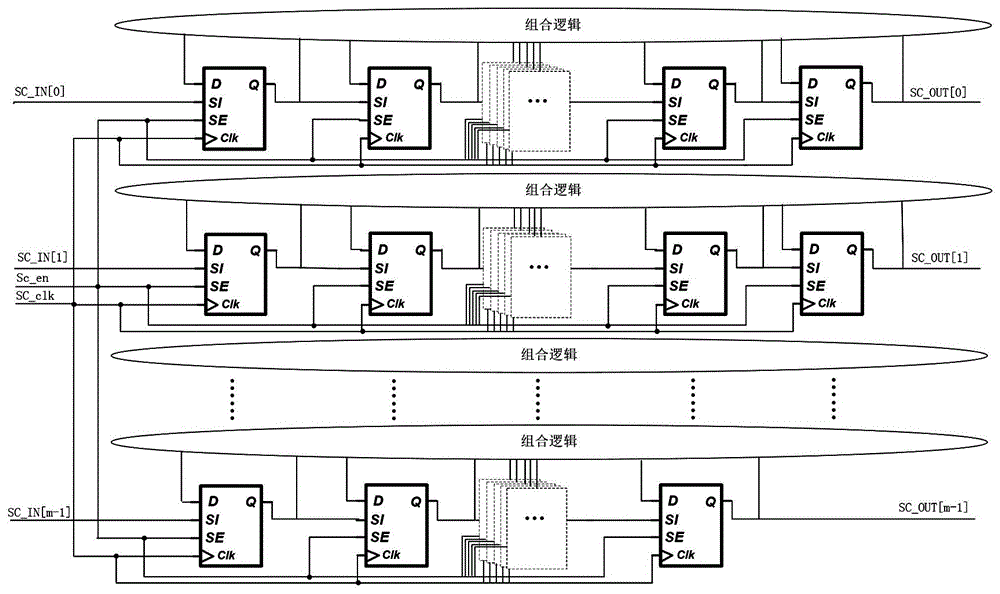

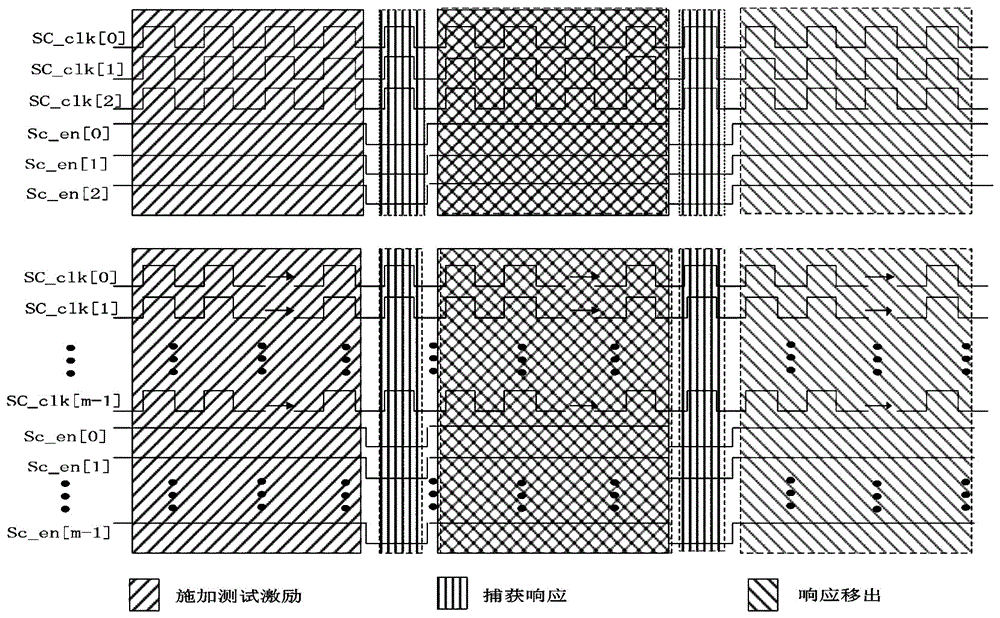

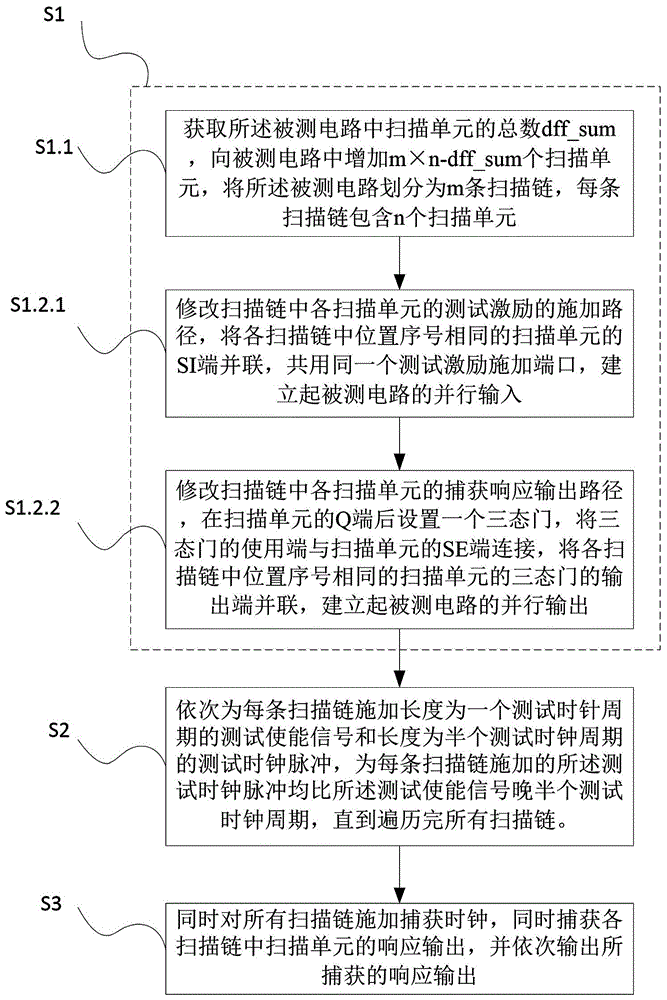

[0054] Such as image 3 As shown, the present embodiment 1. A low-power scanning test method based on parallel application of test excitations includes the following steps: S1. dividing and constructing scanning units in the circuit under test into several equal-length scan chains; S2. Apply test enable signals and test clock pulses to each scan chain in turn until all scan chains have been traversed; S3. Simultaneously apply capture clocks to all scan chains, capture the response output of the scan units in each scan chain at the same time, and output the captured response output. In this draft example, the specific steps of step S1 are: S1.1. Obtain the total number dff_sum of scanning units in the circuit under test, add m×n-dff_sum virtual scanning units to the circuit under test, and divide the circuit under test into There are m scan chains, each scan chain includes n scan units; S1.2. Interrupt the serial path between each scan unit in the scan chain, and establish par...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More