Top gate type thin film transistor and production method thereof

A technology of thin film transistors and manufacturing methods, which is applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve problems such as surface damage of metal oxide semiconductor materials, unstable resistance of source and drain regions, and influence on device stability, etc., to achieve The effect of stable resistance, light surface damage and stable performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] In order to further illustrate the technical means adopted by the present invention and its effects, the following describes in detail in conjunction with preferred embodiments of the present invention and accompanying drawings.

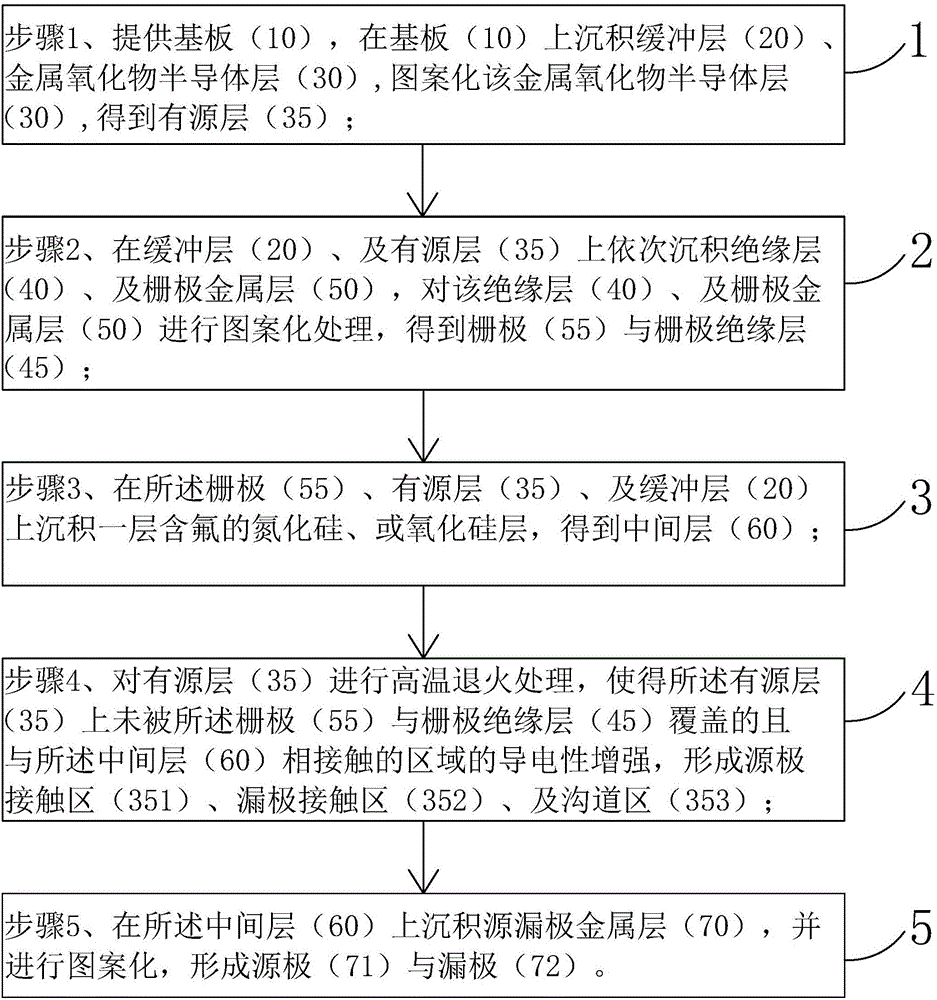

[0037] see figure 1 , the invention provides a method for manufacturing a top-gate thin film transistor, comprising the following steps:

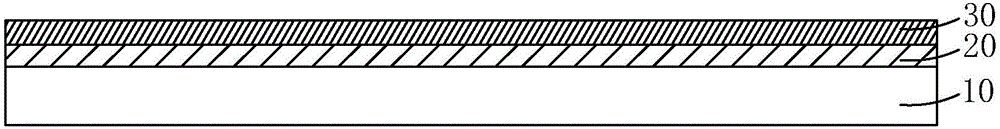

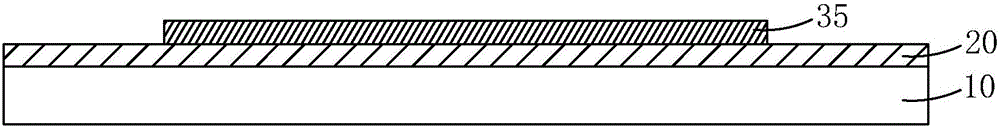

[0038] Step 1, such as Figure 2-3 As shown, a substrate 10 is provided, a buffer layer 20 and a metal oxide semiconductor layer 30 are sequentially deposited on the substrate 10 , and the metal oxide semiconductor layer 30 is patterned to obtain an active layer 35 .

[0039] Specifically, the buffer layer 20 is formed by depositing insulating materials such as silicon oxide and silicon nitride.

[0040] Specifically, the metal oxide semiconductor layer 30 is formed by depositing at least one of zinc oxide-based, indium oxide-based, tin oxide-based and other semiconductor materials.

[0041] Step 2, such...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More