P type layer-based III nitride enhanced HEMT (High Electron Mobility Transistor) and preparation method thereof

A nitride, p-type layer technology, applied in the field of HEMT device preparation technology, can solve the problems of surface defects, under-etching, p-type layer over-etching, etc., achieve precise control of etching depth, reduce surface damage, The effect of reducing the difficulty of implementation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0062] One aspect of the present invention also provides a method for preparing a group III nitride-enhanced HEMT based on a p-type layer, which includes:

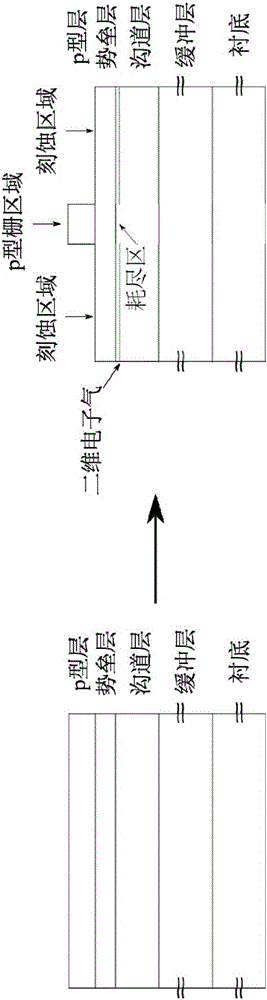

[0063] On the substrate, a first semiconductor layer body as a channel layer, a second semiconductor layer as a barrier layer, and a third semiconductor layer capable of forming a heterojunction with the second semiconductor layer are sequentially grown, wherein, relative to the selected A certain etching substance, the composition material of the region adjacent to the third semiconductor layer in the second semiconductor layer has higher etching resistance than the composition material of the third semiconductor layer,

[0064] Alternatively, the substrate is sequentially grown to form a first semiconductor layer as a channel layer, a second semiconductor layer as a barrier layer, an etching stop layer, and a third semiconductor capable of forming a heterojunction with the second semiconductor layer layer, wherein, relat...

Embodiment 1

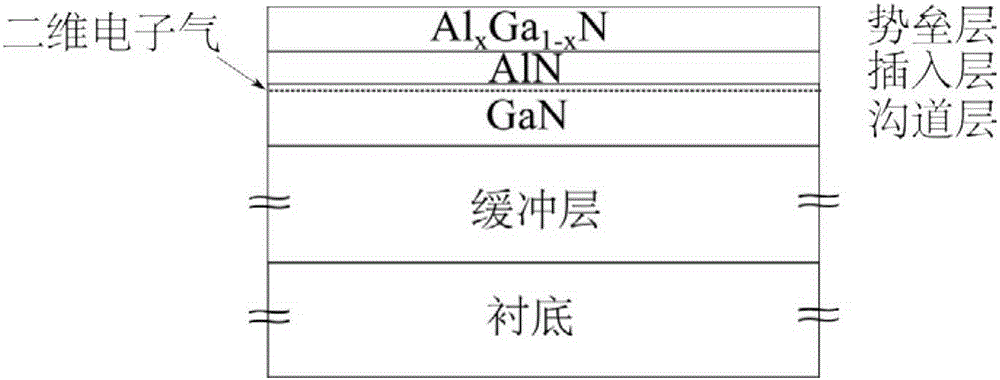

[0075] Embodiment 1 The structure of this HEMT is as Figure 11 As shown, it includes a buffer layer formed on the substrate, Al x Ga 1-x N / GaN heterojunction (x=0.1-0.35), AlN etch stop layer, passivation layer, source electrode (referred to as source), drain electrode (referred to as drain), gate electrode (referred to as gate), etc. Wherein, the substrate may be sapphire, silicon carbide, gallium nitride, aluminum nitride and other substrates, but is not limited thereto. The material of the buffer layer can be commonly used in the industry, for example, GaN, AlGaN, etc. can be used.

[0076] A method for preparing the HEMT provided in this embodiment may include the following steps:

[0077] S1: MOCVD epitaxial growth of HEMT based on AlGaN / GaN heterojunction. Among them, the Al composition x of the AlGaN barrier layer is 10% to 35%, and the thickness is 5 to 25nm; the AlN insertion layer is about 1nm; the GaN channel layer is 50 to 200nm, and the HEMT epitaxial structu...

Embodiment 2

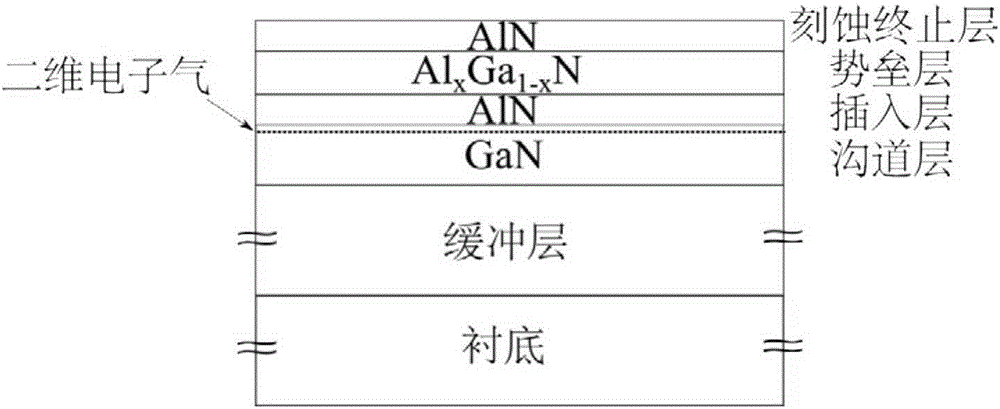

[0087] The structure of embodiment 2 this HEMT is as Figure 14 As shown, it includes a buffer layer formed on the substrate, Al x Ga 1-x N / GaN heterojunction (x=0.1-0.4), passivation layer, source electrode (referred to as source), drain electrode (referred to as drain), gate electrode (referred to as gate), etc. In the barrier layer, the Al composition changes stepwise with the growth z direction, and the high Al composition AlGaN acts as the etch stop layer (Al 0.4 Ga 0.6 N).

[0088] A method for preparing the HEMT provided in this embodiment may include the following steps:

[0089] S1: MOCVD epitaxial growth of HEMT based on AlGaN / GaN heterojunction. Among them, the Al composition x of the AlGaN barrier layer is 10%, 20%, 30%, and 40% along the epitaxial growth z direction, and the thickness of the barrier layer is 5-25nm; the AlN insertion layer is about 1nm; the GaN channel layer is 50~200nm, HEMT epitaxial structure such as Figure 12a-Figure 12b shown.

[009...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More