Method for evaluating single-particle multi-transient soft error sensitivity of combinational logic circuit considering layout information

A combinational logic circuit and sensitivity evaluation technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as the inability to effectively evaluate single-event multi-transient soft error sensitivity, and shorten the simulation time. , to ensure the effect of simulation accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

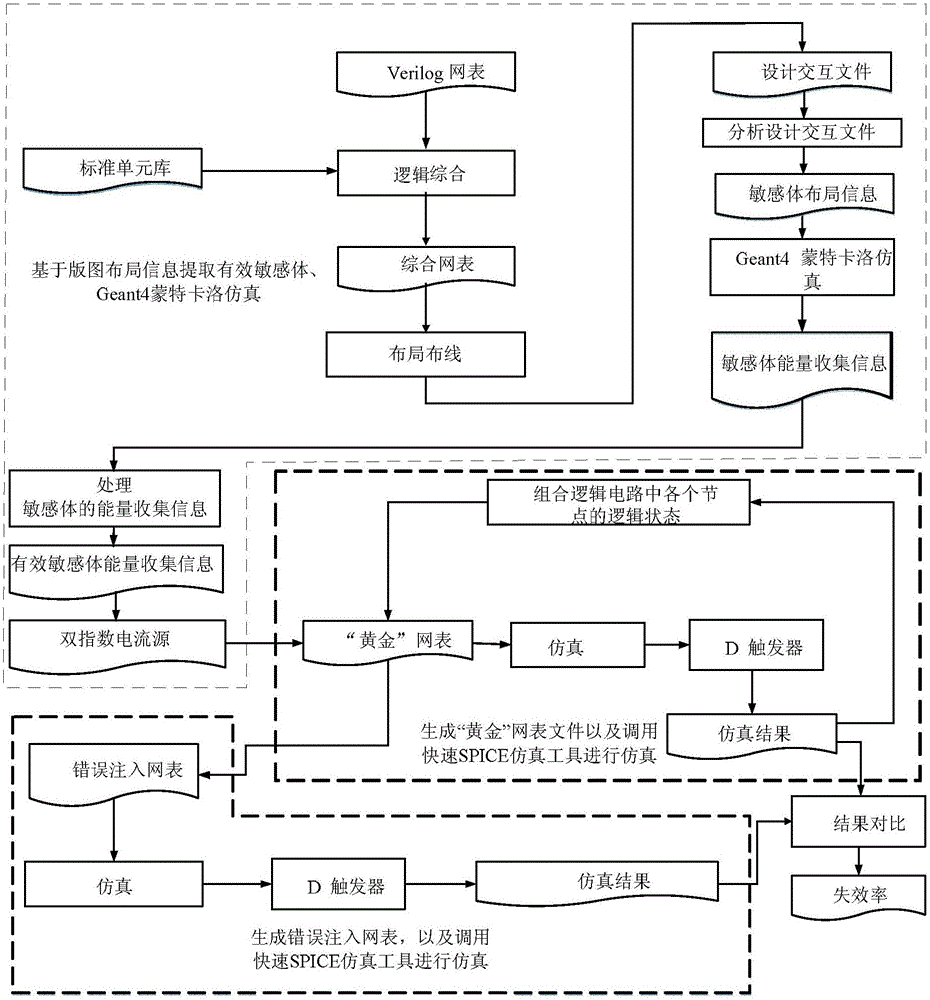

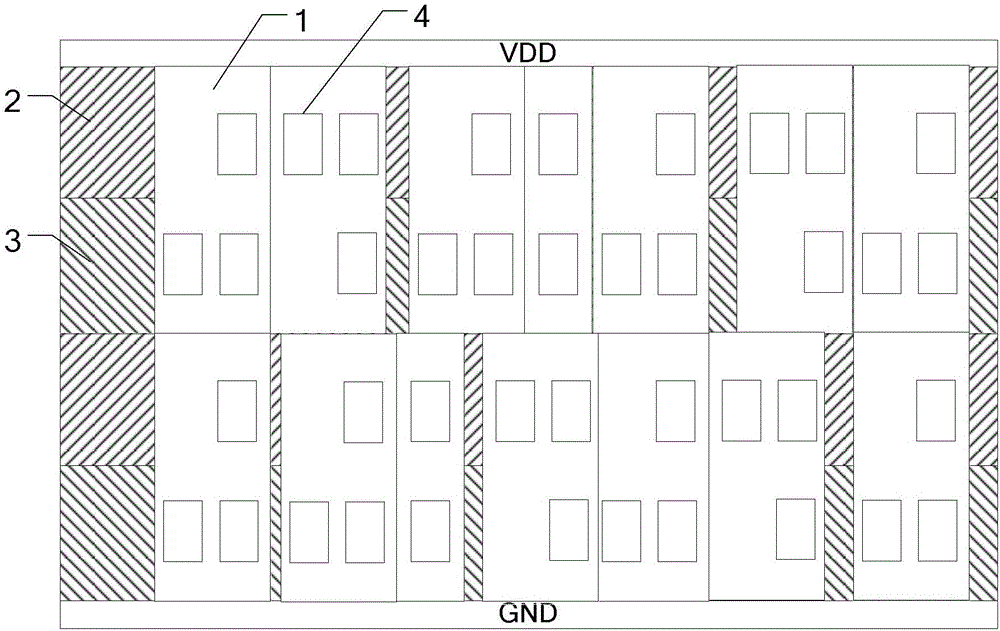

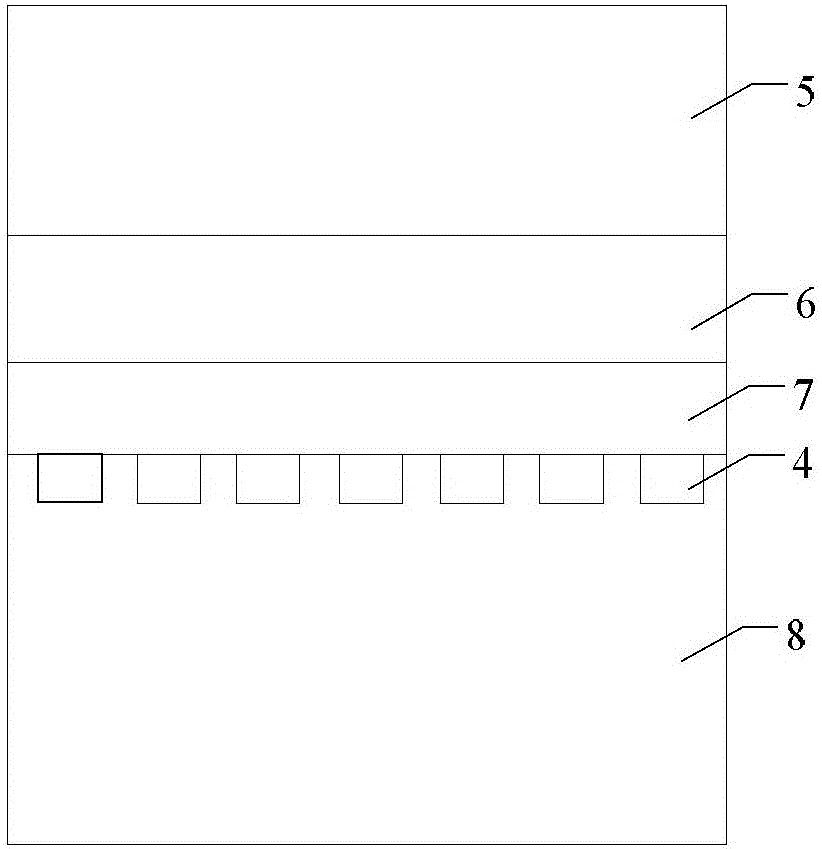

[0034] Specific implementation mode one: combine Figure 1 to Figure 10 Specifically explain this embodiment, a method for evaluating the susceptibility of single event multiple transient soft errors of a combinational logic circuit considering layout information described in this embodiment, the method includes the following steps:

[0035] Step 1. Extract effective sensitive bodies based on layout information, and perform Geant4 Monte Carlo simulation, including the following steps:

[0036] Step 11, based on the standard cell library under the Verilog netlist and the process library, the combinational logic circuit written using the hardware description language is carried out logic synthesis to obtain a comprehensive netlist;

[0037] Step 12, using a layout and routing tool to place and route the integrated netlist, and save the result as a design interactive file;

[0038] Step 13, analyzing the drain position of each transistor in each logic unit of the design interact...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More