Preparation method of semiconductor device

A semiconductor and device technology, applied in the field of semiconductor device preparation, can solve problems such as short circuit between gate and polysilicon layer, uncontrollable distance between polysilicon layers, etc., and achieve the effect of reducing width, avoiding short circuit, and improving process accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

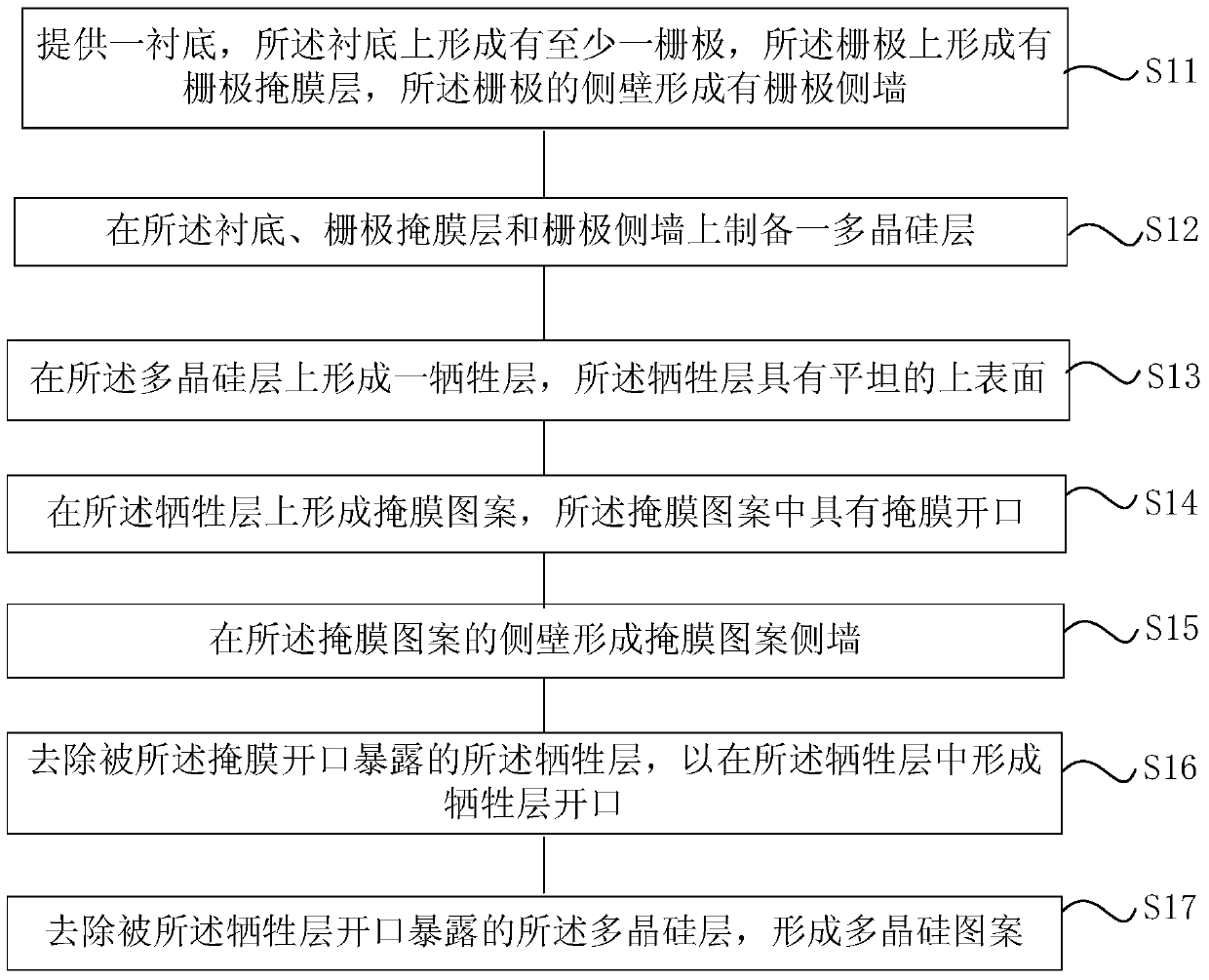

[0040] The core idea of the present invention is to provide a method for preparing a semiconductor device, such as figure 2 shown, including:

[0041] Step S11: providing a substrate, on which at least one gate is formed, a gate mask layer is formed on the gate, and gate sidewalls are formed on the side walls of the gate;

[0042] Step S12: preparing a polysilicon layer on the substrate, the gate mask layer and the gate sidewall;

[0043] Step S13: forming a sacrificial layer on the polysilicon layer, the sacrificial layer having a flat upper surface;

[0044] Step S14: forming a mask pattern on the sacrificial layer, the mask pattern having a mask opening;

[0045] Step S15: forming sidewalls of the mask pattern on the sidewalls of the mask pattern;

[0046] Step S16: removing the sacrificial layer exposed by the mask opening to form a sacrificial layer opening in the sacrificial layer; and

[0047] Step S17: removing the polysilicon layer exposed by the sacrificial la...

no. 1 example

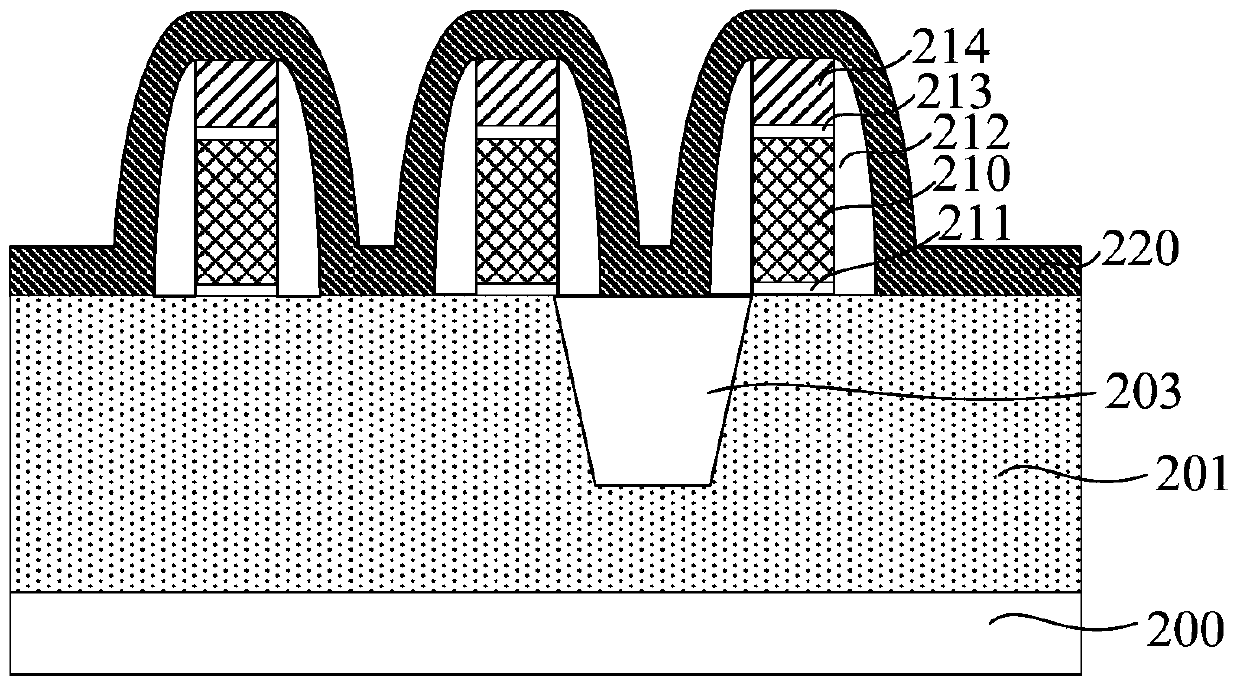

[0051] see Figure 3-Figure 11 The first embodiment of the present invention is specifically described, wherein, Figure 3-Figure 11 It is a schematic diagram of the structure of the semiconductor device in the first embodiment of the present invention during the manufacturing process.

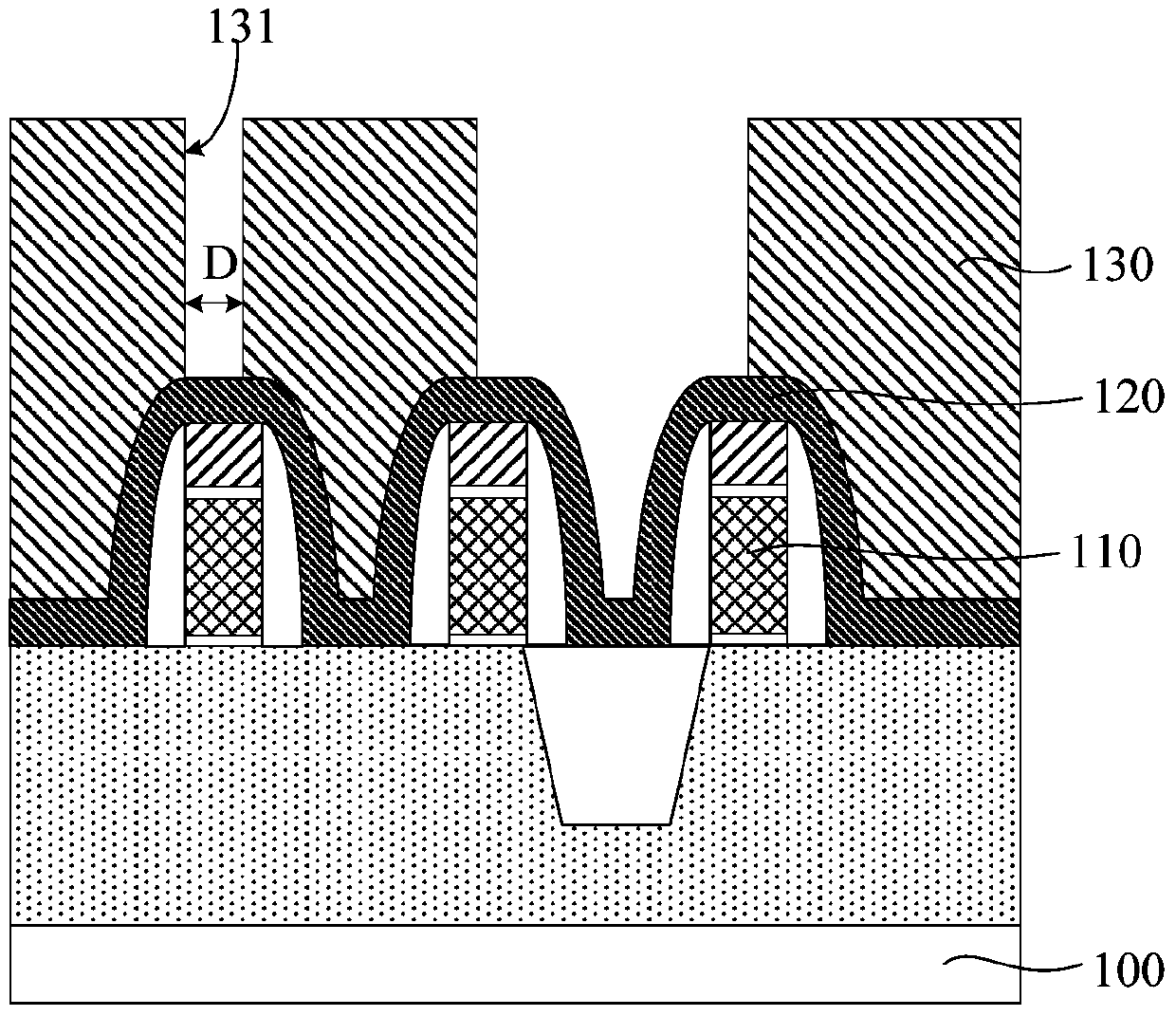

[0052] First, if image 3As shown, step S11 is performed to provide a substrate 200, on which at least one gate 210 is formed, a gate mask layer 214 is formed on the gate 210, and the sidewall of the gate 210 A gate spacer 212 is formed. The substrate 200 includes a well region 201 , and an isolation region 203 is also disposed in the substrate 200 , which is common knowledge in the art and will not be described in detail here. exist image 3 Three gates 210 are shown in , and in other embodiments of the present invention, 2, 4, 5 or more gates 210 may also be disposed on the substrate 200 . In this embodiment, a gate oxide layer 211 may be provided between the substrate 200 and the gate ...

no. 2 example

[0065] see Figure 12-Figure 18 ,in, Figure 12-Figure 18 It is a schematic diagram of the structure of the semiconductor device in the second embodiment of the present invention during the manufacturing process. exist Figure 12-Figure 8 , the reference numerals indicate the same Figure 3-Figure 11 The same expression is the same structure as the first embodiment. The manufacturing method of the semiconductor device of the second embodiment is basically the same as the manufacturing method of the semiconductor device, the difference is that: the material of the sacrificial layer is the same as that of the gate mask layer, and the specific preparation steps are as follows :

[0066] Such as Figure 12 As shown, in the step S11, the material of the gate mask layer 314 is oxide, and the material of the gate spacer 312 is nitride.

[0067] Then go to step S12 and continue to refer to Figure 12 , preparing a polysilicon layer 220 on the substrate 200 , the gate mask layer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More