Single-instruction multi-thread staining cluster structure of uniform staining architecture graphics processor

A graphics processor and single-instruction technology, applied in the direction of processor architecture/configuration, concurrent instruction execution, electrical digital data processing, etc., can solve poor portability, security, reliability, guarantee hidden dangers, and restrict the independent development of display systems and other problems, to achieve the effect of powerful computing power and powerful unified dyeing ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

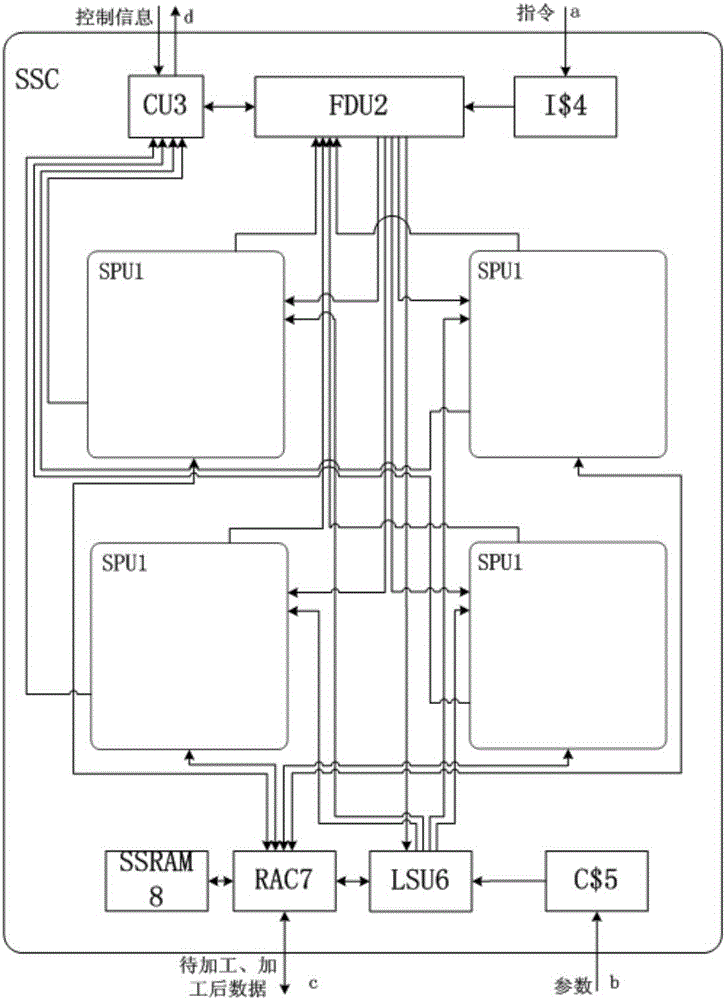

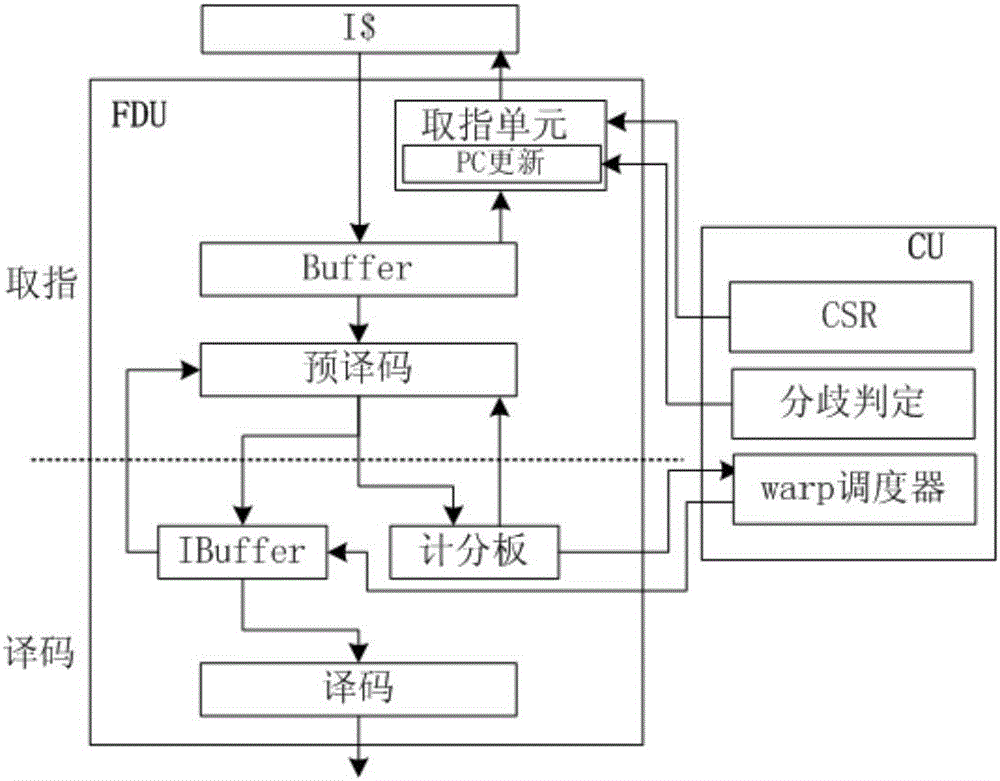

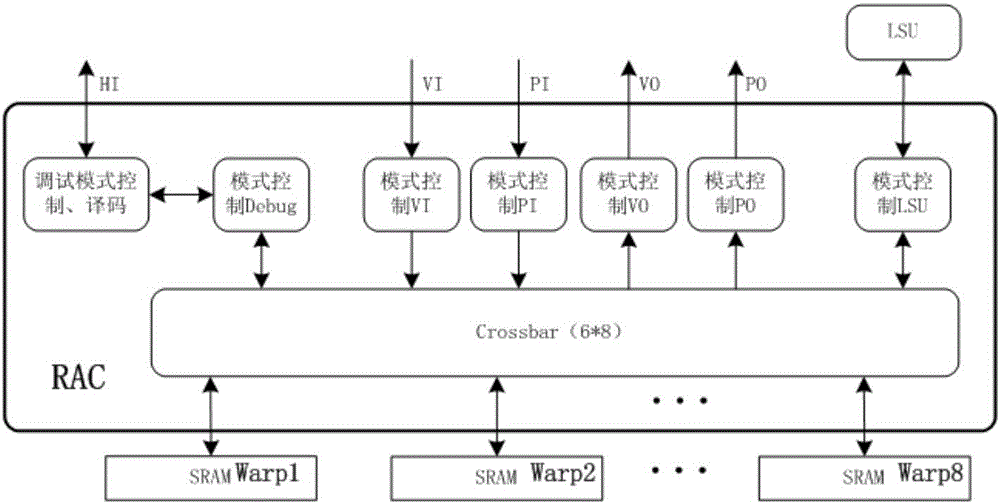

[0055] SSC is the main component of the unified coloring array, the main functional component for vertex and pixel coloring, and the hardware carrier for warp execution. Warp is a collection composed of data to be processed, programs for processing data, and result data after processing. Multiple warps can be executed in time-sharing on the same SSC hardware without interfering with each other. Different warps need to have different on-site record related information, that is, warps need to be supported by corresponding hardware. On SSC: warp data to be processed consists of 16 vertices or pixels that need to be processed in the same way (vertex coloring or pixel coloring); programs for processing data include two categories, namely vertex coloring programs and pixel coloring programs; The resulting data includes vertex-colored output and pixel-colored output. One SSC supports 8 warps, and the SSC can select one of the 8 warps per cycle, and uses dual-issue technology to issu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More