Data packet verification method and data packet verification system

A verification method and verification system technology, applied in transmission systems, user identity/authority verification, electrical components, etc., can solve problems such as difficulty in further improving detection speed and difficulty in checking massive network data packets

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

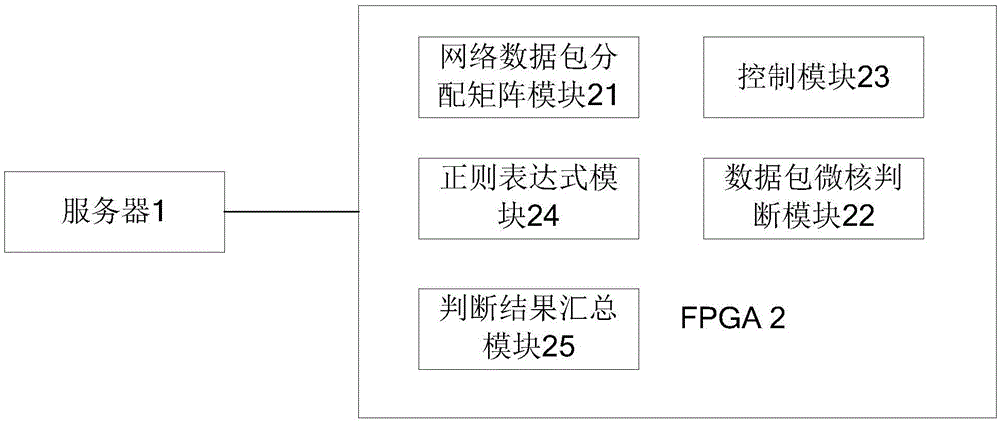

[0042] figure 1 It is a schematic structural diagram of the data packet verification system provided by the first embodiment of the present invention, consisting of figure 1 It can be seen that, in the present embodiment, the data packet verification system provided by the present invention includes: server 1 and FPGA2, and FPGA2 includes network data packet distribution matrix module 21, a plurality of data packet micro-nucleus judgment modules 22, control module 23, regular expression Module 24 and judgment result summary module 25, wherein,

[0043] Server 1 is used to receive the data packet to be verified;

[0044] The network data packet distribution matrix module 21 is used for receiving the data packet to be verified from the server;

[0045] The regular expression module 24 is used to obtain the regular expression for verifying the data packet to be verified;

[0046] The data packet micro-kernel judging module 22 is used to execute the regular expression to verify...

no. 2 example

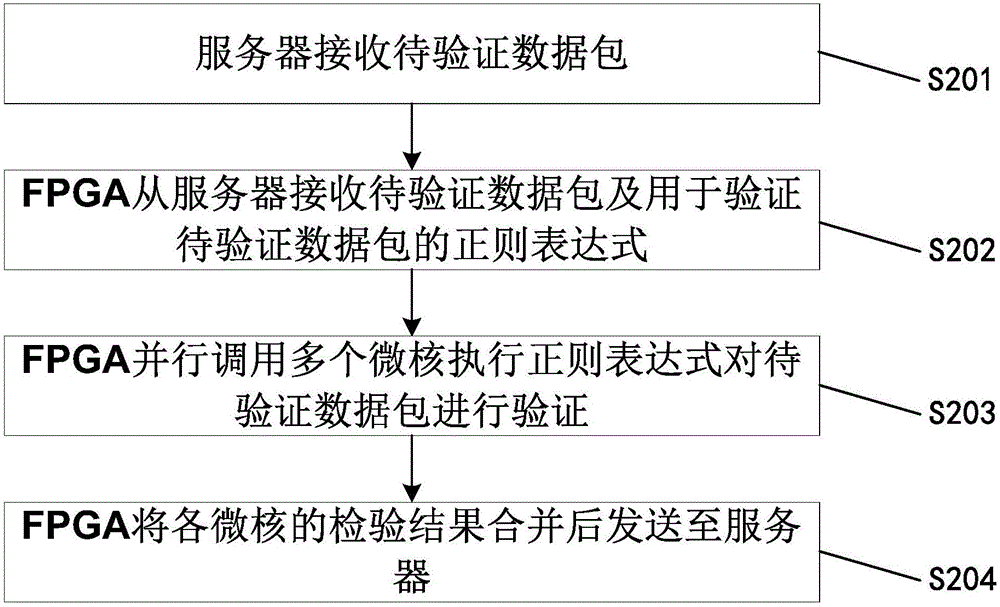

[0055] figure 2 It is a flow chart of the data packet verification method provided by the second embodiment of the present invention, consisting of figure 2 It can be seen that, in this embodiment, the data packet verification method provided by the present invention includes:

[0056] S201: the server receives the data packet to be verified;

[0057] S202: The FPGA receives the data packet to be verified and the regular expression used to verify the data packet to be verified from the server;

[0058] S203: The FPGA invokes multiple microkernels in parallel to execute regular expressions to verify the data packets to be verified;

[0059] S204: The FPGA combines the inspection results of the micronuclei and sends them to the server.

[0060] In some embodiments, before the method in the foregoing embodiment calls a plurality of microkernels in parallel, the FPGA also includes: the FPGA obtains all values of the data packet to be verified, and calls a corresponding number...

no. 3 example

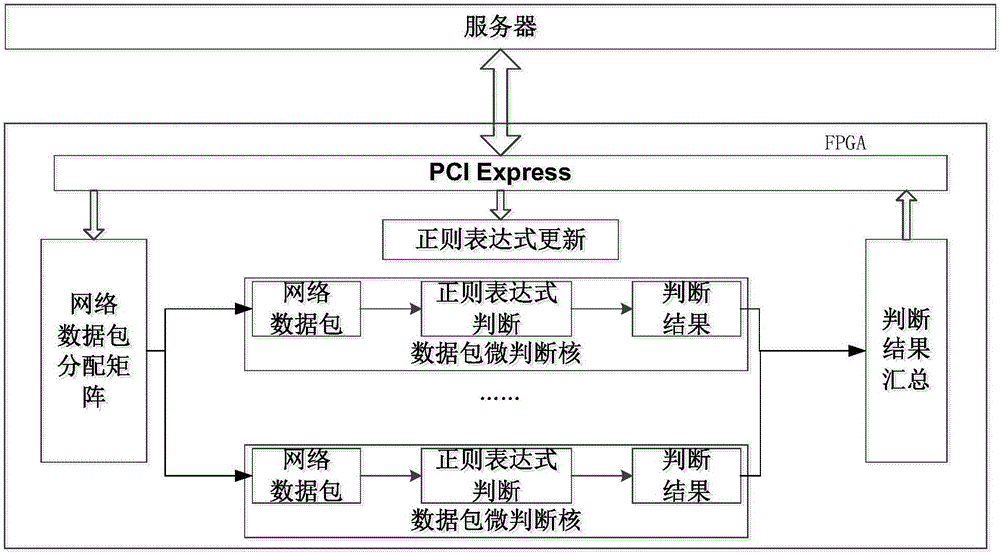

[0073] For regular expressions based on software implementation, instructions are executed in a serial order, and it is difficult to further improve the detection speed. This embodiment provides a new verification system, such as image 3 As shown, the FPGA-based hardware is integrated into the server system with the PCIE bus, reads data and regular expression algorithms from the server according to the instructions of the server, and realizes parallel regular expression verification by instantiating multiple data packet microprocessing cores in parallel. Upload the final test results to the server. This product uses a regular expression algorithm system based on FPGA hardware. First, FPGA uses a function similar to DMA to share the server's processing of network data packets. Secondly, the parallel regular expression algorithm based on FPGA realizes algorithm acceleration in a shorter cycle. Supports high-speed real-time data packet inspection. Finally, FPGA can instantiate ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More