QLED field effect transistor with improved light extraction ratio, and preparation method for QLED field effect transistor

A field-effect transistor and light extraction rate technology, which is used in semiconductor/solid-state device manufacturing, photovoltaic power generation, electric solid-state devices, etc., can solve the problems of low light extraction rate of integrated light-emitting devices, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

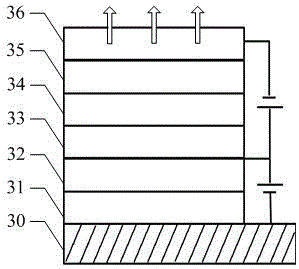

[0041] Such as image 3 As shown, the SOI substrate is cleaned by the standard Shiraki method, including organic solvent ambient ultrasonic, multi-step strong acid treatment, etc. to remove the surface insulating layer and organic impurities and metal element impurities. The SOI substrate sequentially includes a first silicon layer 30 , an insulating layer 31 and a second silicon layer 32 from bottom to top.

[0042] The first silicon layer 30 can be N-type doped, the first silicon layer 30 is used as the first electrode, the first electrode is the cathode of the FET, and the gate of the FET at the same time.

[0043] The insulating layer 31 can choose PMMA or polyimide (PI) material. For example, when choosing PI material, PI and N,N-dimethylformamide (DMF) can be diluted at a volume ratio of 1:1 and spin coated on the first silicon layer 30. Then dry in an infrared box for 5 minutes, and then anneal for 3 hours in an argon atmosphere at 220°C.

[0044] Etching is performe...

Embodiment 2

[0050] Such as Figure 4 As shown, the SOI substrate is cleaned by the standard Shiraki method, including organic solvent ambient ultrasonic, multi-step strong acid treatment, etc. to remove the surface insulating layer and organic impurities and metal element impurities. The SOI substrate includes a first silicon layer 40 , an insulating layer 41 and a second silicon layer 42 sequentially from bottom to top.

[0051] The first silicon layer 40 can be N-type doped, the first silicon layer 40 is used as the first electrode, and the first electrode is the anode of the FET and also the gate of the FET.

[0052] The insulating layer 41 can be made of PMMA or polyimide (PI). For example, when choosing PI material, PI and N,N-dimethylformamide (DMF) can be diluted at a volume ratio of 1:1 and spin coated on the first silicon layer 40. Then dry in an infrared box for 5 minutes, and then anneal for 3 hours in an argon atmosphere at 220°C.

[0053] Etching is performed on the surfac...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More