Semiconductor wafer test method, projection manufacturing method, semiconductor device and electronic device

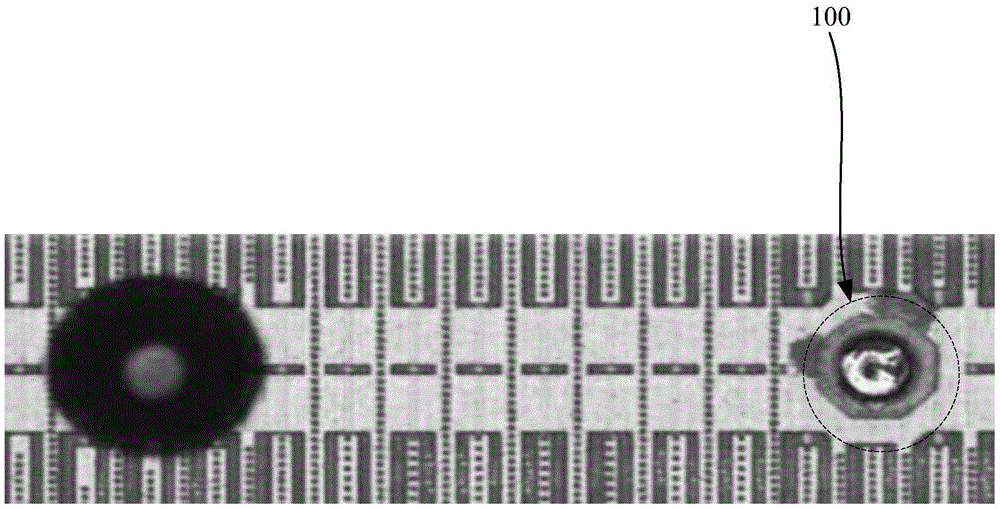

A technology of wafer testing and manufacturing methods, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device testing/measurement, etc., and can solve problems such as pollution, influence of ball bottom metal layer bump process, and missing bumps , to achieve the effect of avoiding missing bumps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

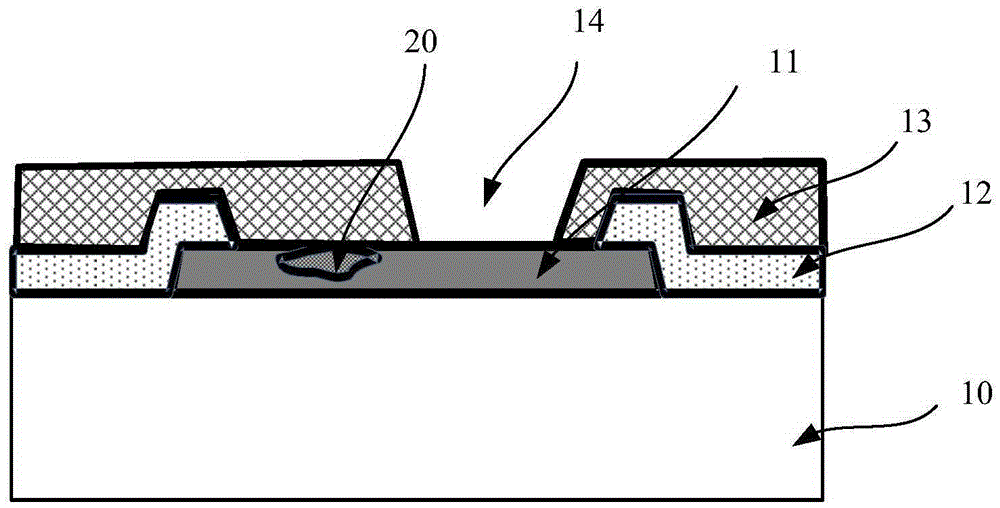

[0032] Below, refer to Figures 4A to 4D and Figure 5 A method for manufacturing wafer bumps according to an embodiment of the present invention will be specifically described. in, Figure 4A to Figure 4D A cross-sectional view of a structure formed in the relevant steps of a wafer bump manufacturing method according to an embodiment of the present invention; image 3 It is a flowchart of a method for manufacturing wafer bumps according to an embodiment of the present invention.

[0033] The method for manufacturing wafer bumps according to Embodiment 1 of the present invention includes the following steps:

[0034] Step S101 , providing a semiconductor wafer, forming bonding pads and a first passivation layer covering the semiconductor wafer and exposing the bonding pads on the semiconductor wafer.

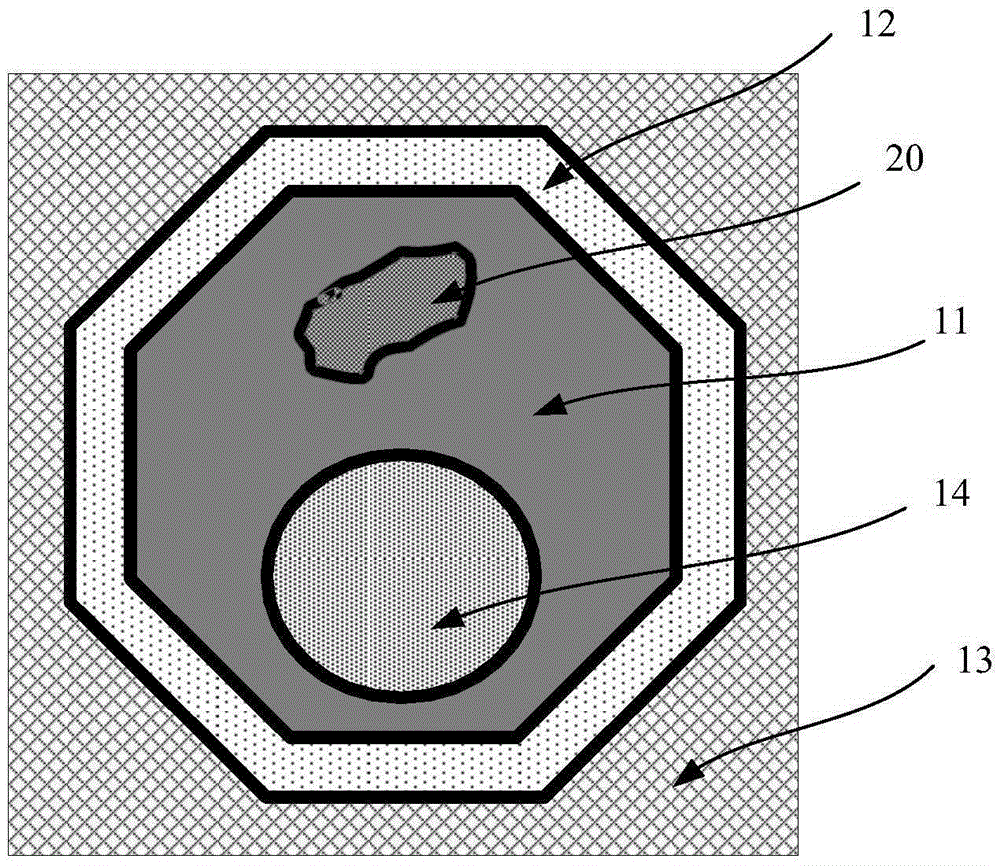

[0035] Such as Figure 4A As shown, a semiconductor wafer 10 is provided on which pads 11 and a first passivation layer 12 covering the semiconductor wafer 10 and exposing ...

Embodiment 2

[0058] Another embodiment of the present invention provides a semiconductor device, which can be prepared by the above-mentioned method.

[0059] Such as Figure 6 As shown, the semiconductor device 100 of this embodiment includes a semiconductor element 101 with a functional circuit and a packaging substrate 103, and the semiconductor element 101 and the packaging substrate 103 are connected by bumps 102 formed on the semiconductor element 101, wherein the The bump 102 is formed by the wafer bump manufacturing method provided by the present invention.

[0060] Wherein, the semiconductor element 101 may be an integrated circuit device for implementing various functions, such as various processor chips such as microprocessors and DSPs, or audio and video decoding chips, and the like.

[0061] The semiconductor device of this embodiment has high packaging reliability.

Embodiment 3

[0063] Still another embodiment of the present invention provides an electronic device, including a semiconductor device and an electronic component connected to the semiconductor device. Wherein, the semiconductor device is the above-mentioned semiconductor device.

[0064] Wherein, the electronic component may be any electronic component such as a discrete device or an integrated circuit.

[0065] The electronic device of this embodiment can be any electronic product or equipment such as mobile phone, tablet computer, notebook computer, netbook, game console, TV set, VCD, DVD, navigator, camera, video recorder, voice recorder, MP3, MP4, PSP, etc. , can also be any intermediate product including the semiconductor device.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More