Data window search method and circuit

A data window and query method technology, applied in the field of FPGA, can solve the problem that the LVDS interface cannot receive high-speed data correctly and stably

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

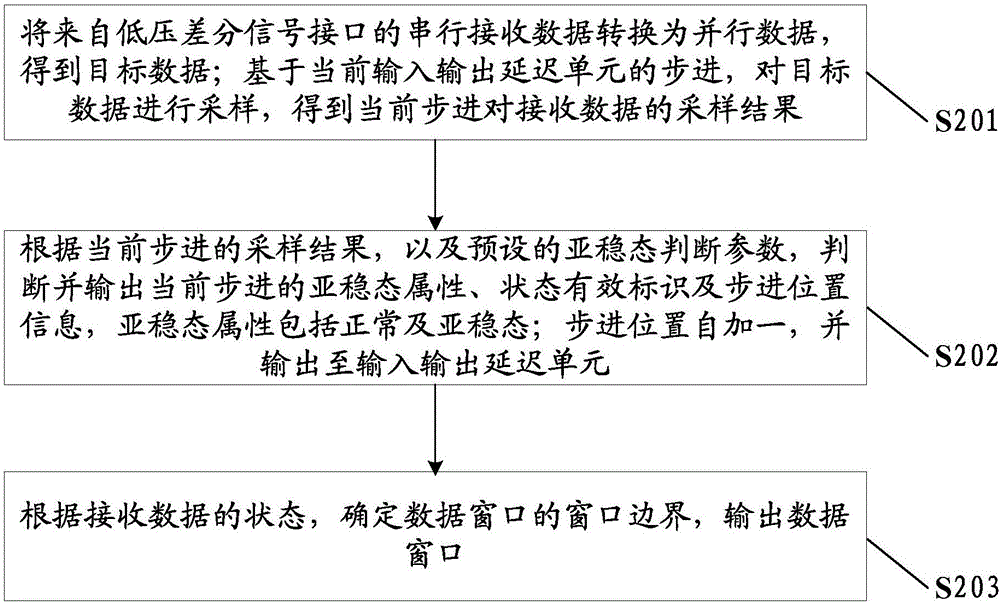

[0034] figure 2 The flow chart of the data window query method provided by the first embodiment of the present invention is composed of figure 2 It can be seen that, in this embodiment, the data window query method provided by the present invention includes the following steps:

[0035] S201: Convert the serial received data from the low-voltage differential signal interface into parallel data to obtain target data; based on the step of the current input and output delay unit, sample the target data to obtain the sampling result of the received data at the current step;

[0036] S202: According to the sampling result of the current step and the preset metastable state judgment parameters, judge and output the metastable state attribute of the current step, the effective state identification and the step position information, the metastable state attribute includes normal and metastable state; the step position is incremented by one, and output to the input and output delay ...

no. 2 example

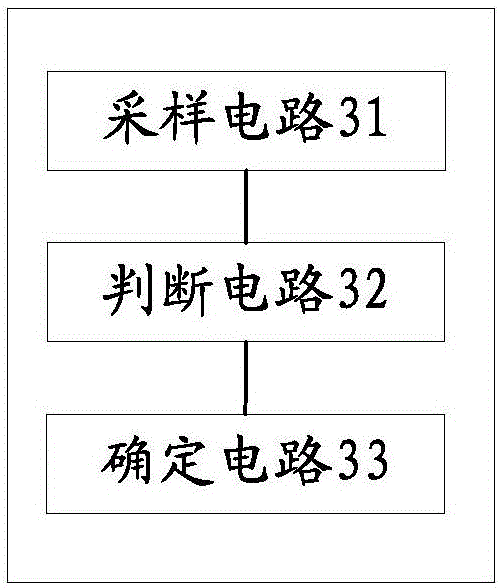

[0043] image 3 A schematic structural diagram of the data window query circuit provided for the second embodiment of the present invention, by image 3 It can be seen that in this embodiment, the data window query circuit provided by the present invention includes:

[0044] The sampling circuit 31 is used to convert the serial received data from the low-voltage differential signal interface into parallel data to obtain the target data, based on the step of the current input and output delay unit, sample the target data to obtain the current step to the received data Sampling results;

[0045] The judging circuit 32 is used to judge and output the metastable property of the current step, the effective state identification and the step position information according to the sampling result of the current step and the preset metastable state judgment parameter. The metastable property includes Normal and metastable; the step position is incremented by one, and output to the inp...

no. 3 example

[0053] The present invention will be further explained in combination with specific application scenarios.

[0054] All current FPGAs have an IODELAY unit whose function is to adjust the delay of data circulating on the IO. The adjustment method can implement a fixed-value delay by setting fixed parameters, or dynamically adjust the data delay through the internal logic of the FPGA.

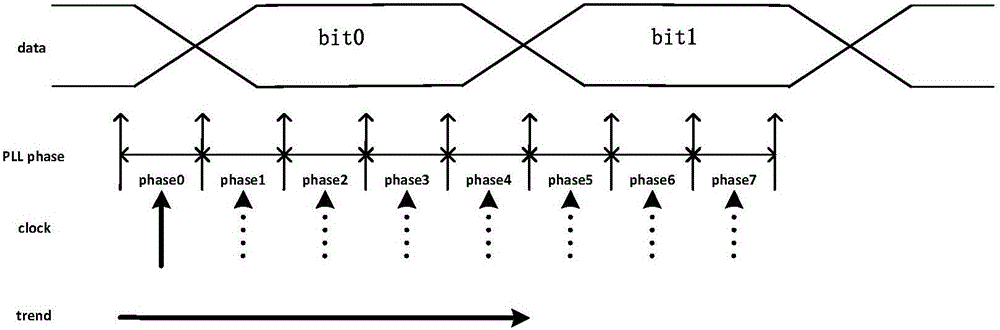

[0055] To solve the problem of low adjustment accuracy caused by adjusting the PLL phase, and to avoid sampling deviation caused by PLL jitter, this embodiment introduces a method of querying the data window by dynamically adjusting IODELAY. This method uses the sampling clock as a reference, and changes the sampling point by adjusting the phase of the data relative to the sampling clock. The adjustment range of this method is 128 steps, and the time width of each step is 25ps. If the data is transmitted at a rate of 700Mbps and in DDR mode, it is necessary to adjust 56 steps to traverse one bi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More