Method for forming fin field-effect transistor

A fin-type field effect and transistor technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of transistor performance to be improved, and achieve the effect of improving interface performance, improving stability, and thin thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

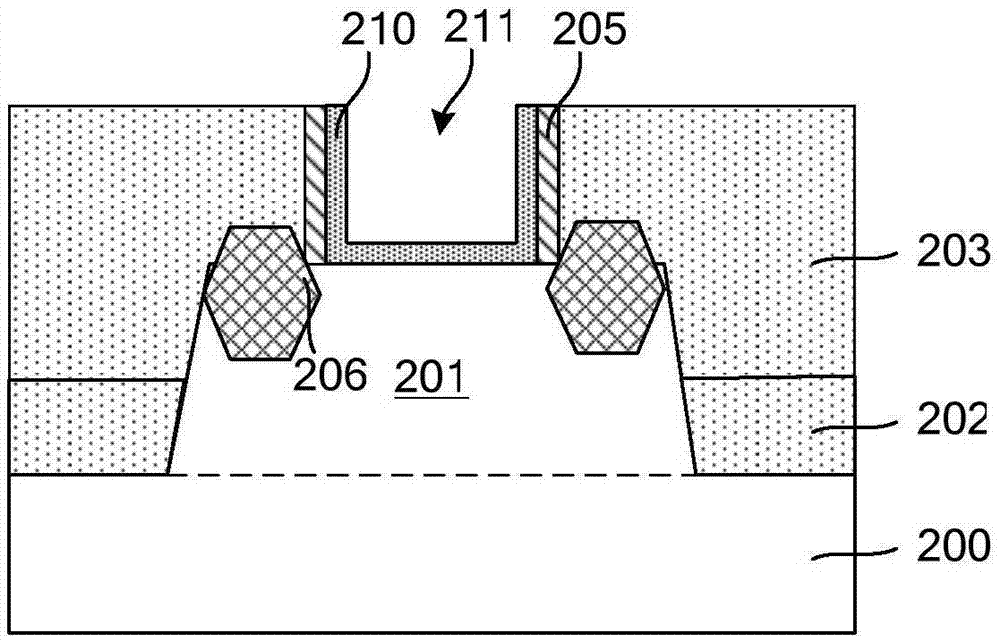

[0027] As mentioned in the background art, the performance of the existing fin field effect transistor still needs to be improved. To improve interface performance, it is necessary to form an interface layer on the surface of the fin before forming the high-K gate dielectric layer.

[0028] The study found that the existing interface layer is generally formed by oxidation process or deposition, and the material of the interface layer is GeO 2 , but GeO formed by prior art 2 The interface layer is very unstable and easily soluble in water, especially when exposed to air, it is easy to react with water vapor in the air; and because of the special structure of the fins, it is difficult to control the thickness of the interface layer, and the uniformity of the thickness It is also difficult to guarantee, and it is difficult to form a thinner thickness of GeO 2 interface layer.

[0029] Therefore, the present invention provides a method for forming a fin field effect transistor....

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More