Semiconductor packaging part and manufacturing method therefor

A semiconductor and packaging technology, applied in the field of semiconductor packaging to prevent warping and its manufacturing, can solve problems such as limited and limited thickness, and achieve the effects of improving durability, controlling warping, and solving unevenness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] Hereinafter, embodiments of the present invention will be described in detail with reference to the accompanying drawings. In the drawings, in order to clearly show main elements related to the inventive concept, the shapes of layers or regions may be exaggerated, and minor elements may be omitted to avoid ambiguity of expression. The inventive concept is not limited to the following embodiments, and the features, elements or structures involved in each embodiment or corresponding method descriptions can be applied to other embodiments individually or in combination.

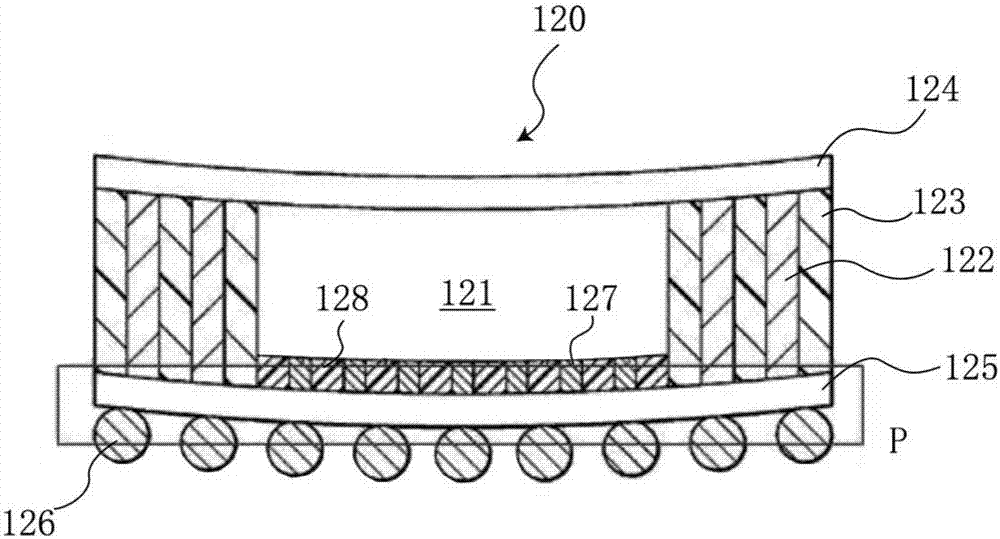

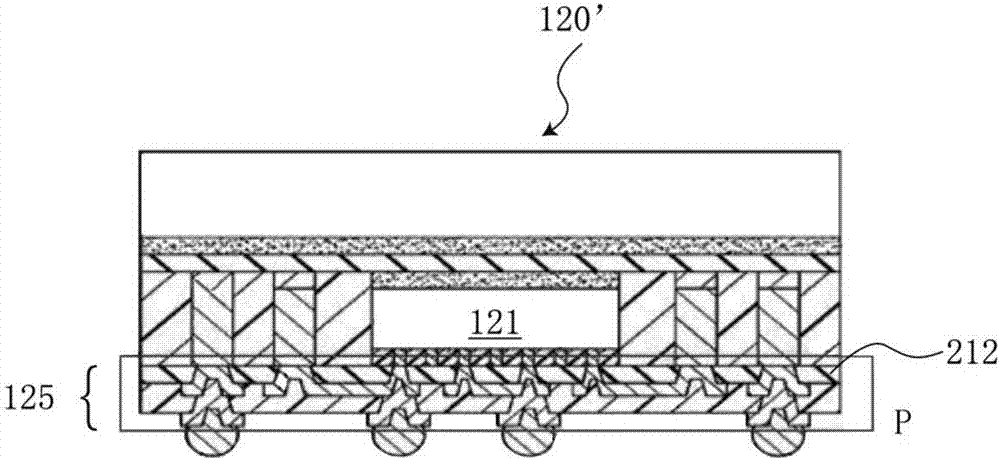

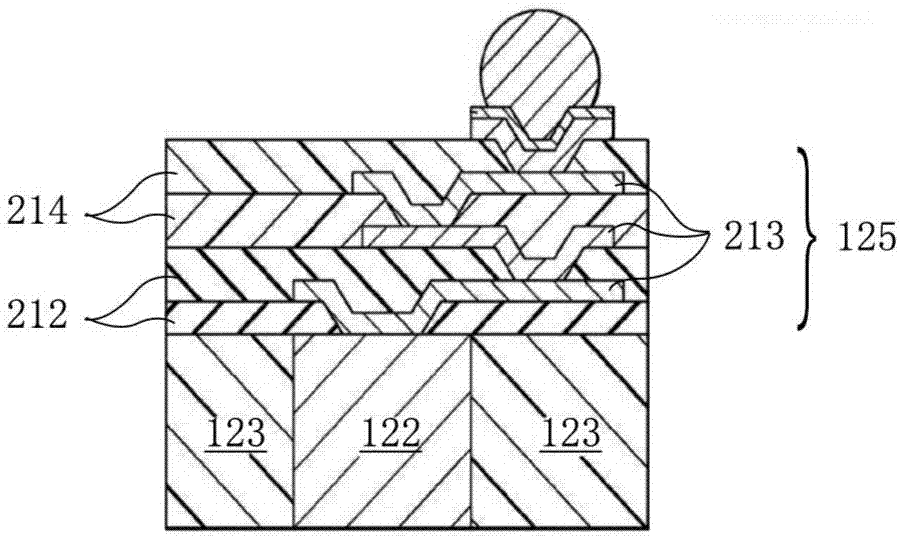

[0030] Figure 4 is a schematic diagram of a semiconductor package according to an embodiment of the present invention. Such as Figure 4 As shown, the semiconductor package 100 includes a substrate 110 , a dielectric layer 120 , a redistribution structure 130 , a semiconductor chip 140 and an encapsulation layer 150 . The substrate 110 is formed of molding material. In one embodiment, the substrate 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More