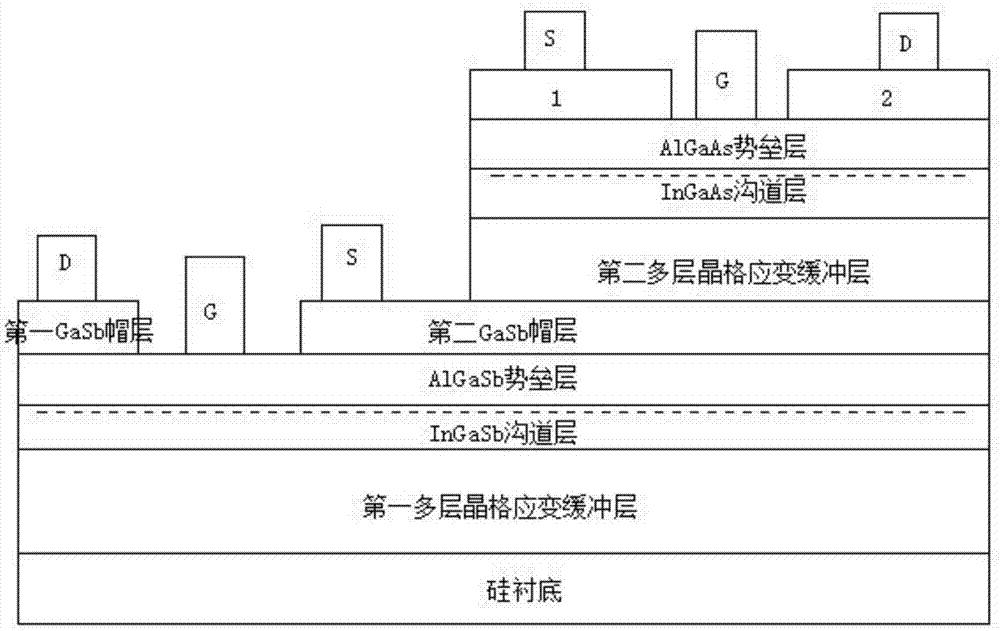

III-V CMOS type persudomorphic heterojunction field effect transistor

A heterojunction field effect and transistor technology, applied in the direction of transistors, electric solid-state devices, semiconductor devices, etc., can solve difficult problems such as reducing power consumption, avoiding lattice relaxation, and overcoming the difficulty of matching atomic lattices Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] In order to make the purpose, technical solution and advantages of the present application clearer, the present application will be further described in detail below in conjunction with the accompanying drawings and specific embodiments. For simplicity, some technical features known to those skilled in the art are omitted from the following description.

[0019] like figure 1 As shown, this embodiment provides a III-V CMOS type pseudo-heterojunction field effect transistor, which is epitaxially grown by MOCVD or MBE equipment, and includes a P-channel transistor and an n-channel transistor; the P-channel transistor is formed on a silicon substrate The first multi-layer lattice strain buffer layer, the InGaSb channel layer and the AlGaSb barrier layer are epitaxially grown in sequence, the first GaSb cap layer and the second GaSb cap layer are grown on the AlGaSb barrier layer, and the InGaSb channel layer and the AlGaSb A two-dimensional hole gas is formed in a region ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More