Check point technology-based dual pipeline and fault tolerance method

A pipeline and checkpoint technology, which is applied to the redundancy in the operation for data error detection, response error generation, error detection/correction, etc., can solve the problems of processor performance degradation, low performance overhead, and inability to locate. Achieve the effect of reducing logic delay, increasing working frequency, and reducing complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] This embodiment describes the specific implementation of the present invention in conjunction with an embedded microprocessor LEON2 with a SPARC V8 architecture. The embedded microprocessor LEON2 of the SPARC V8 architecture adopts a 32-bit RISC architecture, and its pipeline unit is a classic five-stage pipeline, and each pipeline stage of the pipeline performs data interaction with the instruction cache, data cache and register file.

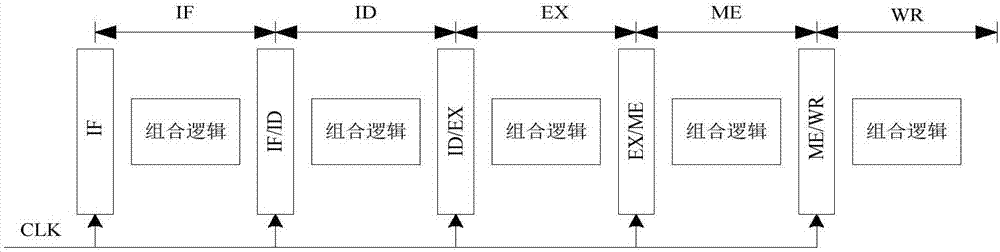

[0027] The pipeline unit of the LEON2 processor includes five combinatorial logic units of instruction fetch (IF), decode (ID), execution (EX), memory access (ME), and write back (WR), as well as five logic units set between each pipeline stage. Group inter-level registers IF, IF / ID, ID / EX, EX / ME, ME / WR, its structure is as follows figure 1 shown. A single event bombards the combinatorial logic part of the pipeline and causes a SET failure, which may be latched by an interstage register and cause a pipeline error. A single event bomba...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More