Coated chip dimension packaging structure and packaging method thereof

A chip size packaging and packaging method technology, applied in electrical components, electrical solid devices, circuits, etc., can solve the problems of unprotected sidewalls, chip offset lithography, chip corner stress, etc., to enhance bonding force, improve Yield, effect of enhancing stress rupture strength

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

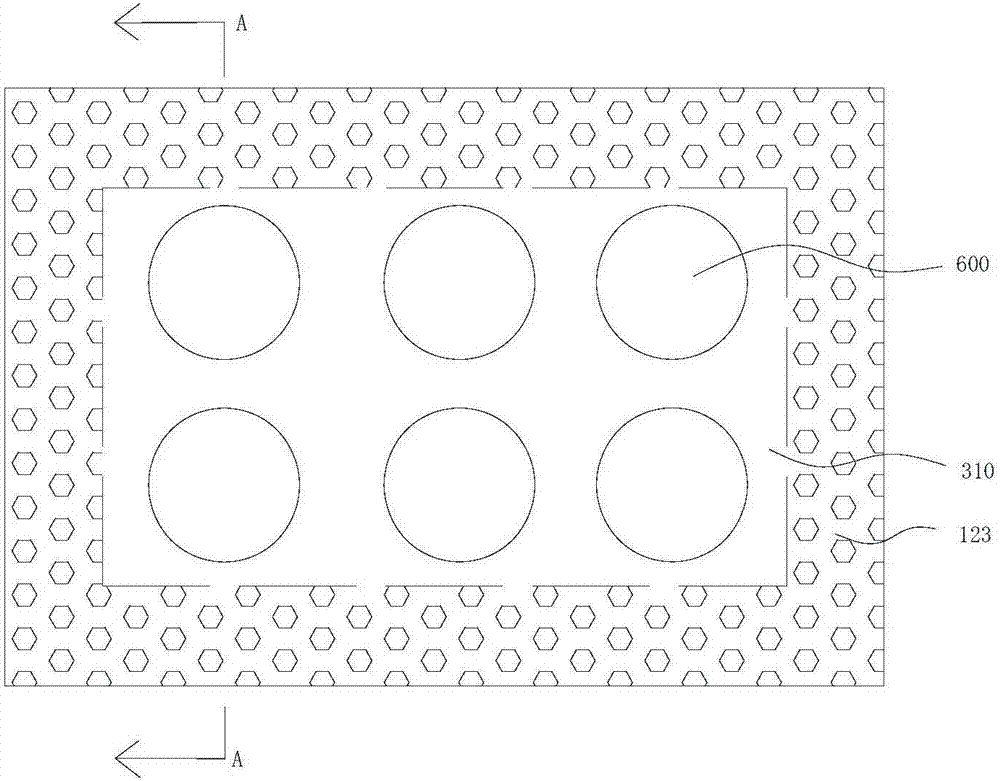

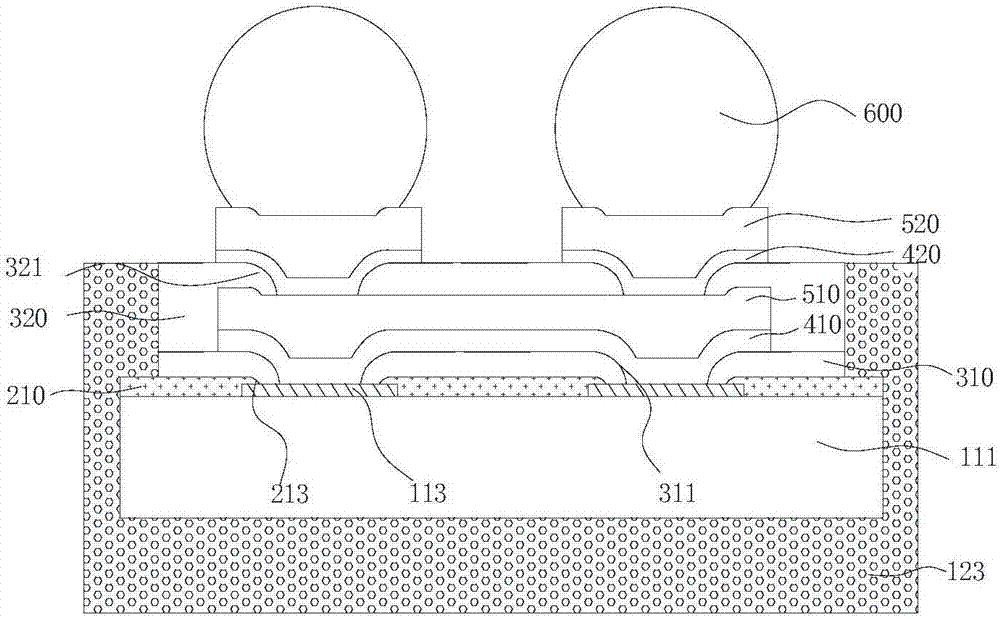

[0061] figure 1 It is a schematic front view of an embodiment of a wrap-around chip-scale packaging structure of the present invention, figure 2 Its A-A sectional schematic diagram.

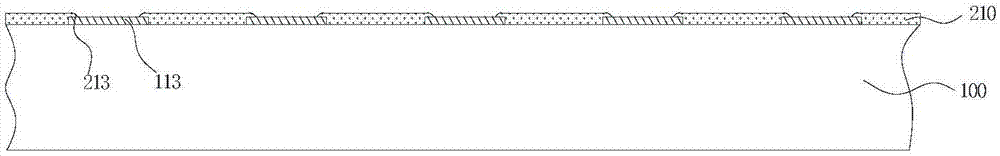

[0062] The present invention is an encapsulation type chip size packaging structure, in which a passivation layer 210 is provided on the front side of the silicon base body 111 and a passivation layer opening 213 is opened, the chip electrode 113 is embedded in the front side of the silicon base body 111 from the back side, and the passivation layer opening 213 exposes the front surface of the chip electrode 113 .

[0063]The upper surface of the passivation layer 210 is provided with a dielectric layer I310 and an opening I311 of the dielectric layer I is provided. The opening I311 of the dielectric layer I exposes the front surface of the chip electrode 113, and the dielectric layer I310 does not cover the edge of the passivation layer 210. The metal seed layer I 410 , the metal layer I 510 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More