Verification method, device, electronic equipment and storage medium for logic circuit design

A technology of logic circuits and verification methods, applied in computing, electrical digital data processing, instruments, etc., can solve problems such as difficult debugging, complex algorithm models, and low operating efficiency, achieve good scalability, improve verification efficiency, and avoid coding work Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

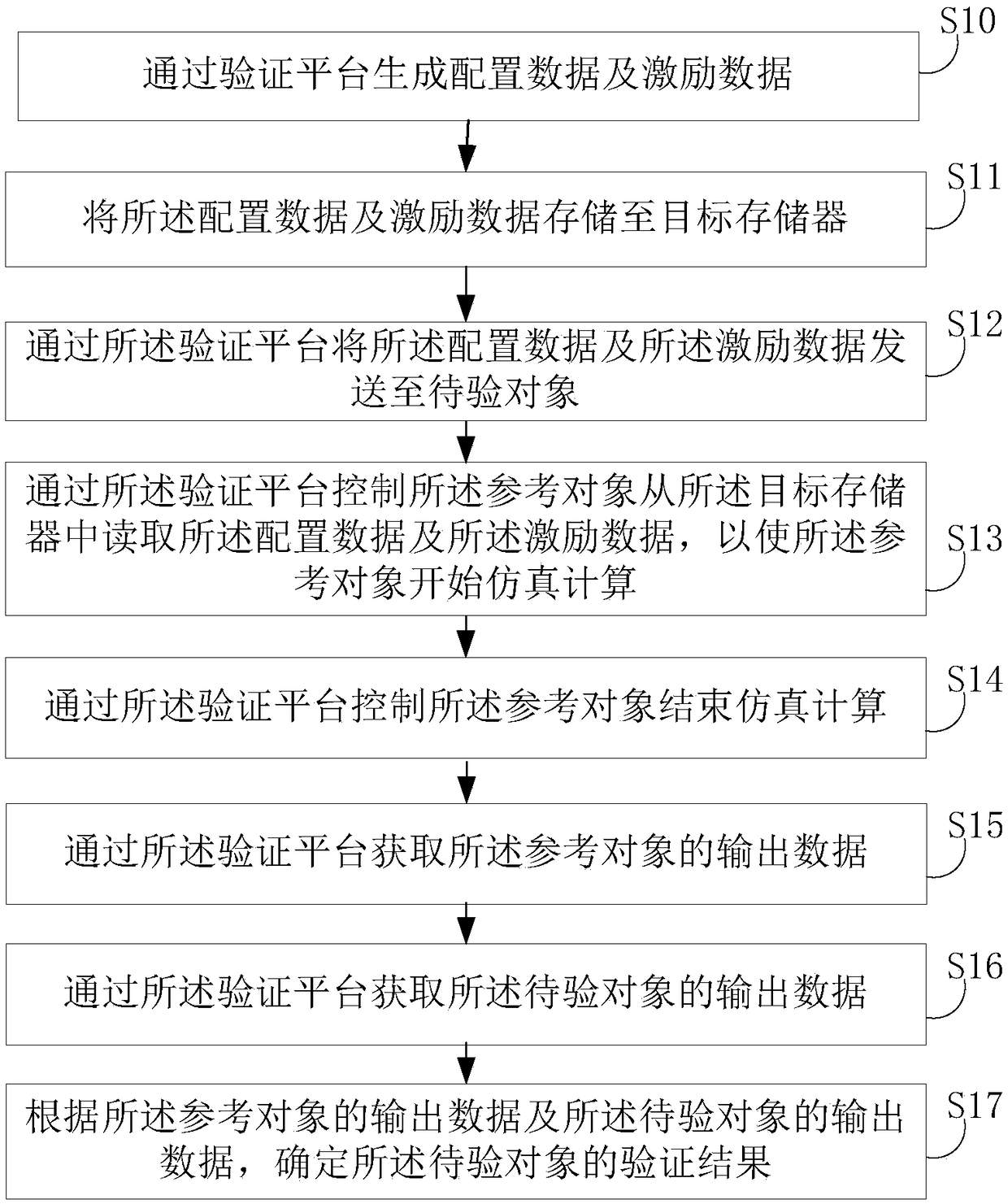

[0045]The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0046] In order to make the above objects, features and advantages of the present invention more comprehensible, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

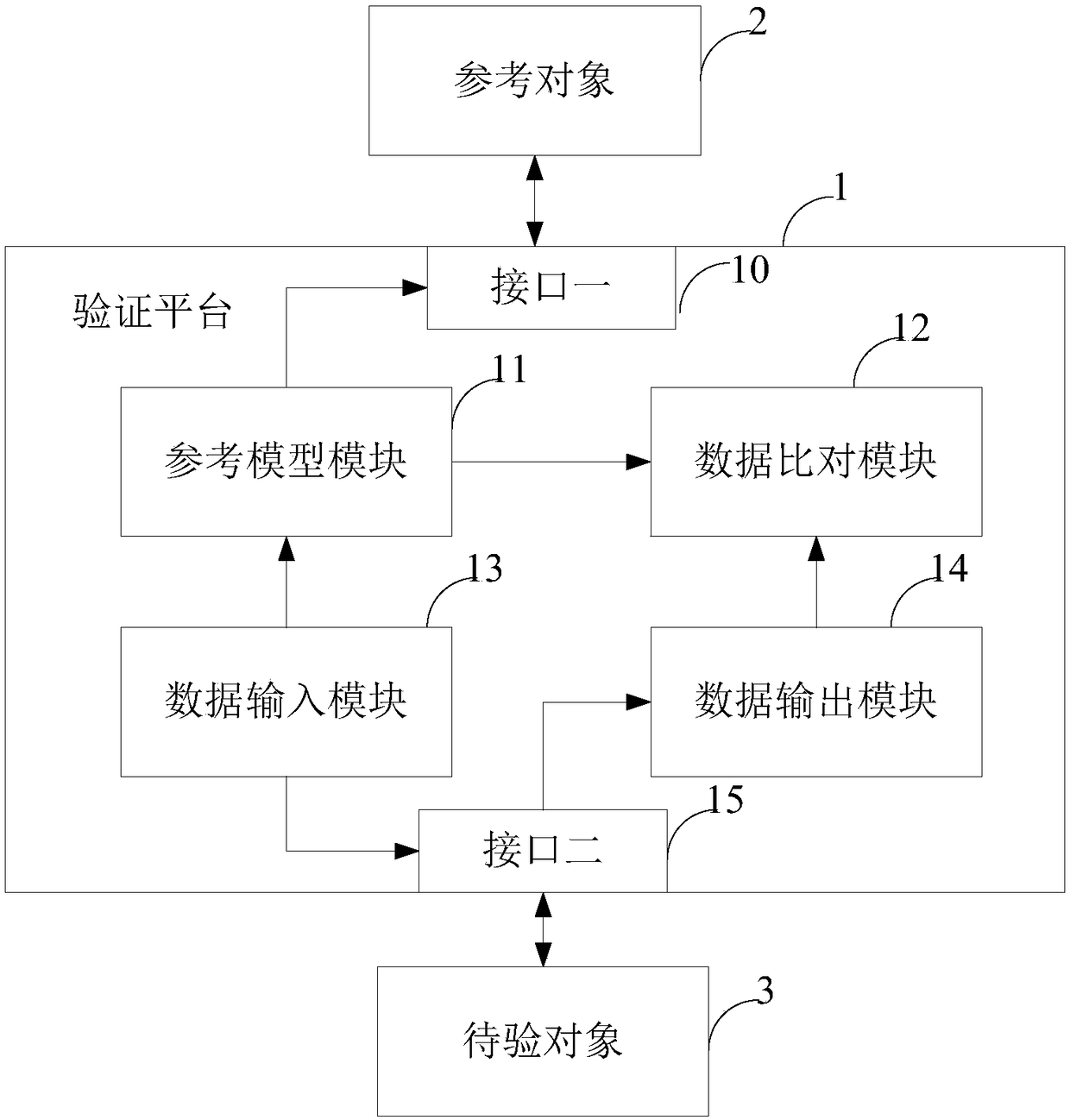

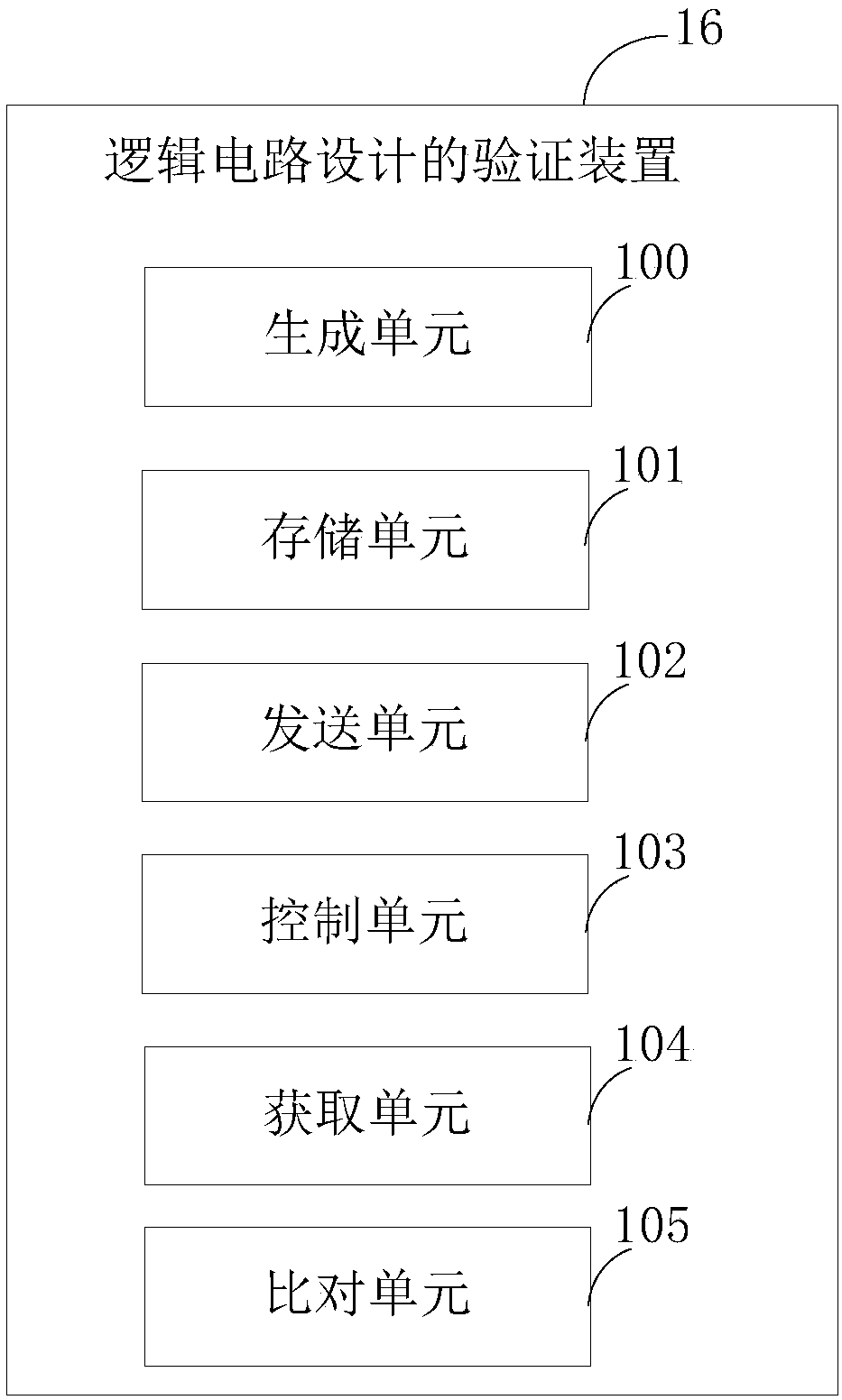

[0047] Such as figure 1 as shown, figure 1 It is a system architecture diagram of a preferred embodiment of the verification method for realizing logic circuit design of the present invention. In this preferred e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More