A FPGA-based multi-board array parallel decryption device and method

A multi-board, array technology, applied in the direction of security communication devices, digital transmission systems, electrical components, etc., can solve the problems of limiting cracking efficiency and performance, increasing cracking performance, etc., to reduce data transmission time and improve data transmission The effect of bandwidth and strong versatility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

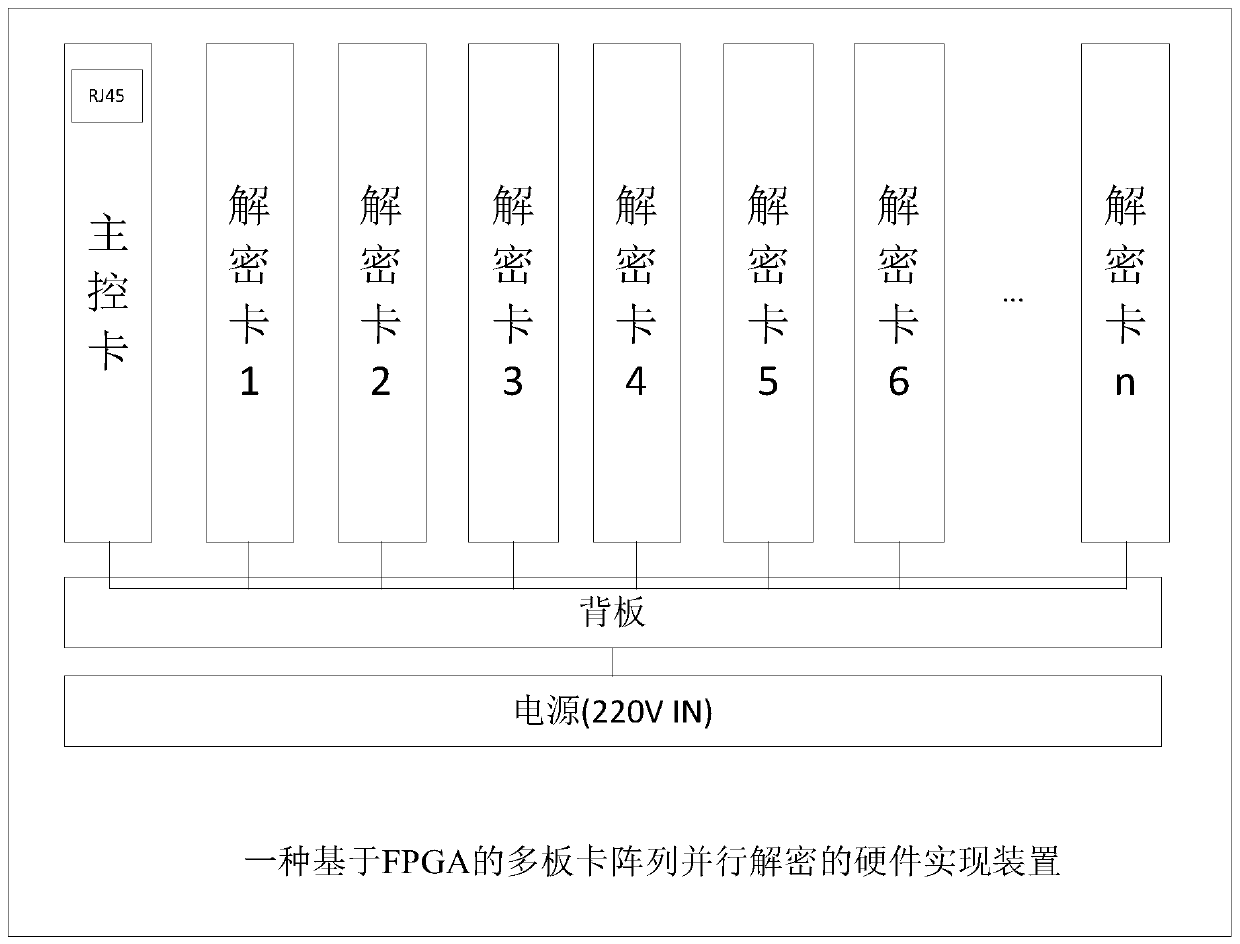

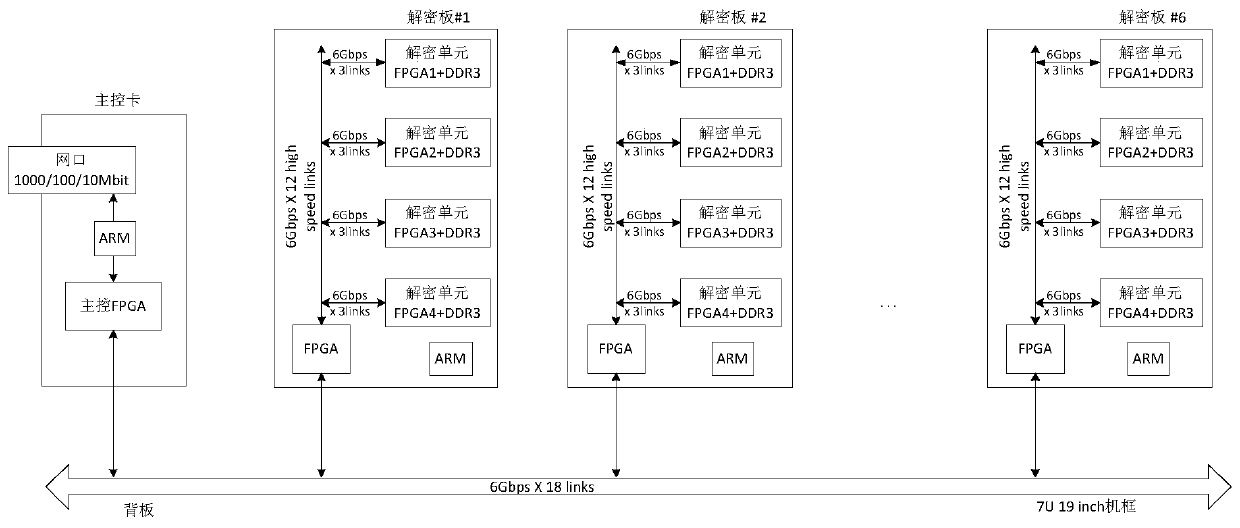

[0024] The FPGA-based multi-board array parallel decryption device disclosed in this embodiment adopts the communication architecture of CPCI, and is interconnected through a high-speed backplane in the form of multiple (not less than 6) FPGA board arrays, so as to realize the decryption of the entire system operations and data processing. Considering the scheduling control and external interconnection of the system, a main control card is set up in the implementation of the scheme to be responsible for external interconnection and scheduling control. attached figure 1 A frame diagram of the parallel decryption device is given. The entire parallel decryption device is composed of three types of boards, namely the decryption card, the main control card and the backplane, and their functions are as follows:

[0025] 1. The main control card is mainly responsible for the external communication and the management and scheduling control of the decryption card.

[0026] 2. Decryp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More