eeprom unit simulation model and eeprom array simulation model

A technology of simulation model and comparison unit, which is applied in the direction of instrumentation, calculation, electrical digital data processing, etc., and can solve problems such as poor continuity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

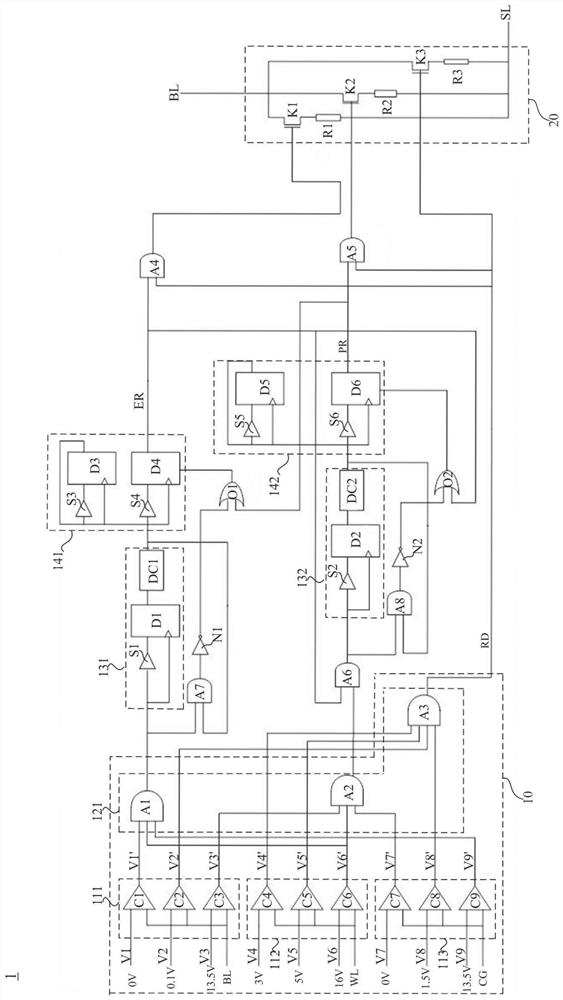

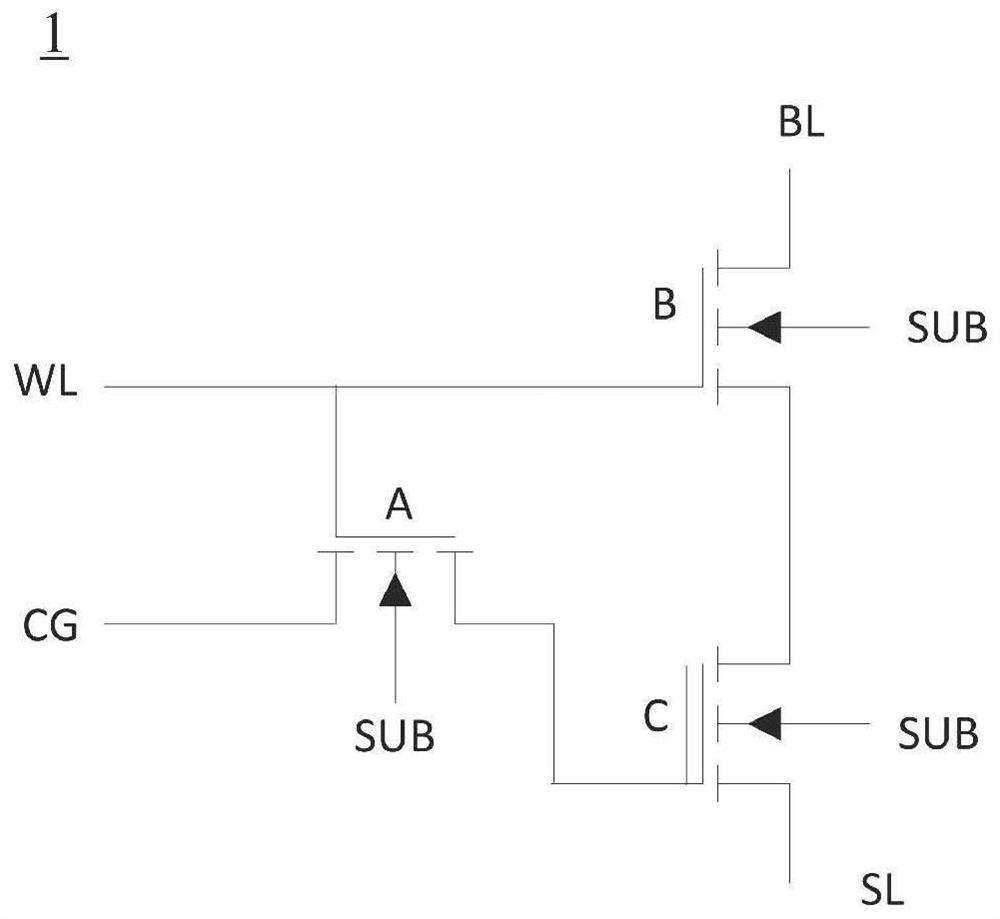

[0040] When the EEPROM unit simulation model in the prior art is used for full-chip simulation verification, functional timing verification and data verification need to be performed separately. The inventor found out from the research of the prior art that there are two types of single-pipe netlist definitions in the existing EEPROM unit simulation model, namely P type and E type, corresponding to 0 unit and 1 unit. When performing full-chip simulation verification, because the storage unit cannot automatically change the internal storage data according to changes in voltage and external input signals, the two are often verified separately and are not completely covered in the same simulation process. When performing functional timing verification of functional modules, usually only focus on the logic changes of internal important signals, and temporarily ignore the feedback to the data unit, but when performing data verification, the opposite is true. Therefore, functional t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com