CMOS transconductance unit circuit with wide input voltage range and high linearity

A voltage range and high linearity technology, applied in the direction of electrical components, logic circuits, logic circuit connection/interface layout, etc., can solve the problems of small input voltage space, high power consumption and hardware cost, and reachability, and achieve wide Effects of input range, high linearity, and simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

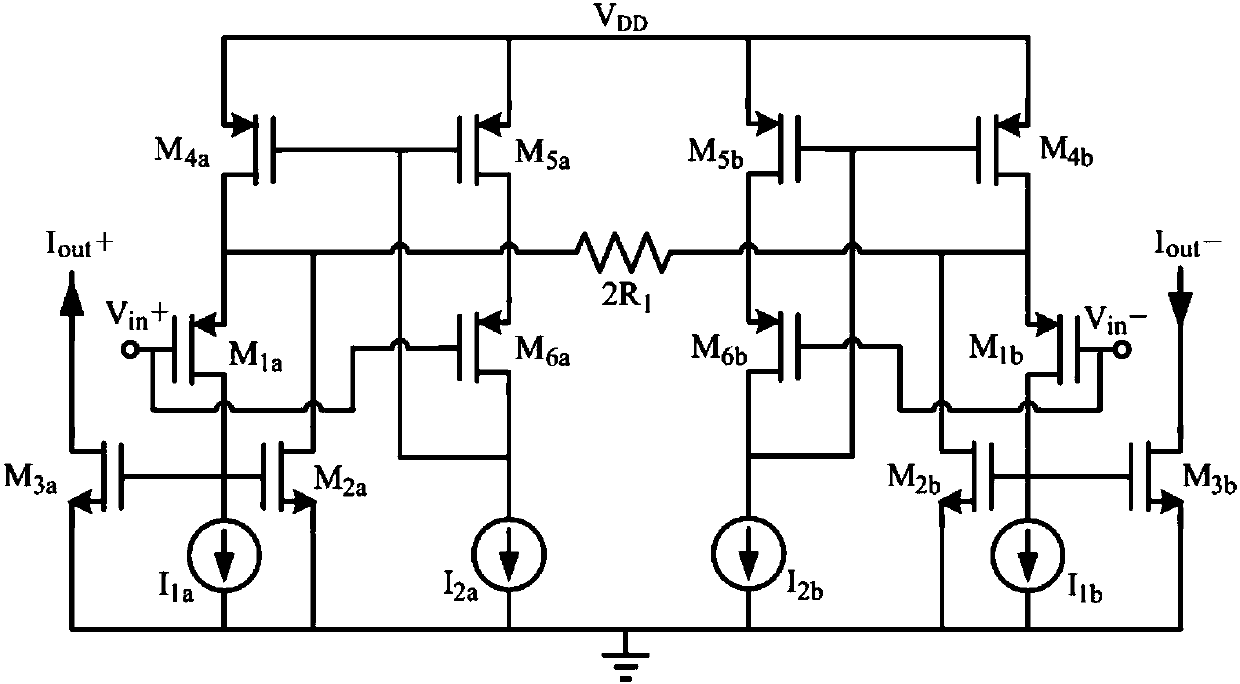

[0027] see figure 2 As shown, a wide input voltage range high linearity CMOS transconductance unit circuit, which includes a bias constant current source, a differential input stage, and an output current mirror,

[0028] The bias constant current source includes a first PMOS transistor M4a, a second PMOS transistor M5a matching the first PMOS transistor M4a, a third PMOS transistor M5b and a fourth PMOS transistor M4b matching the third PMOS transistor M5b, the The sources of the first PMOS transistor M4a, the second PMOS transistor M5a, the third PMOS transistor M5b and the fourth PMOS transistor M4b are connected to the power supply VDD, and the gate of the first PMOS transistor M4a is connected to the gate of the second PMOS transistor M5a and are commonly connected to the output terminal of the first current source I2a, the gate of the third PMOS transistor M5b is connected to the gate of the fourth PMOS transistor M4b and are commonly connected to the output terminal of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More