Multiple-valued heat-insulation multiplier unit circuit based on transmission gate structure

A unit circuit and multiplier technology, which is applied in the direction of instruments, electrical digital data processing, digital data processing components, etc., can solve the problems of multiplier unit circuit area, power consumption and operation cycle, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

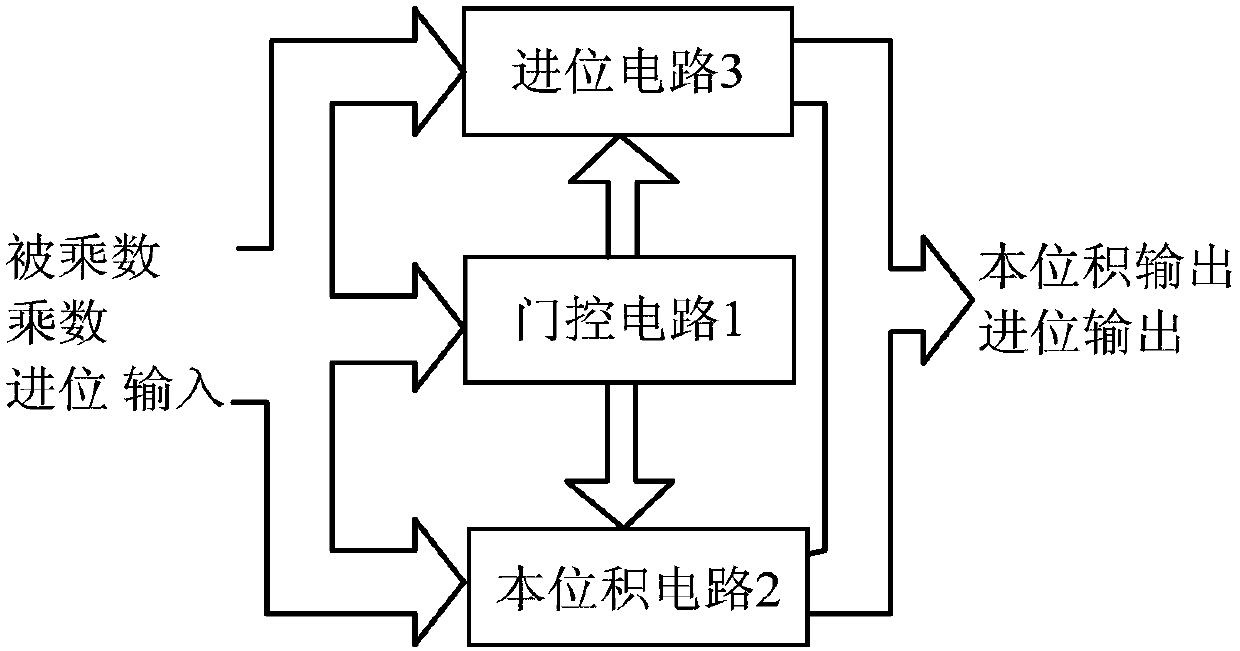

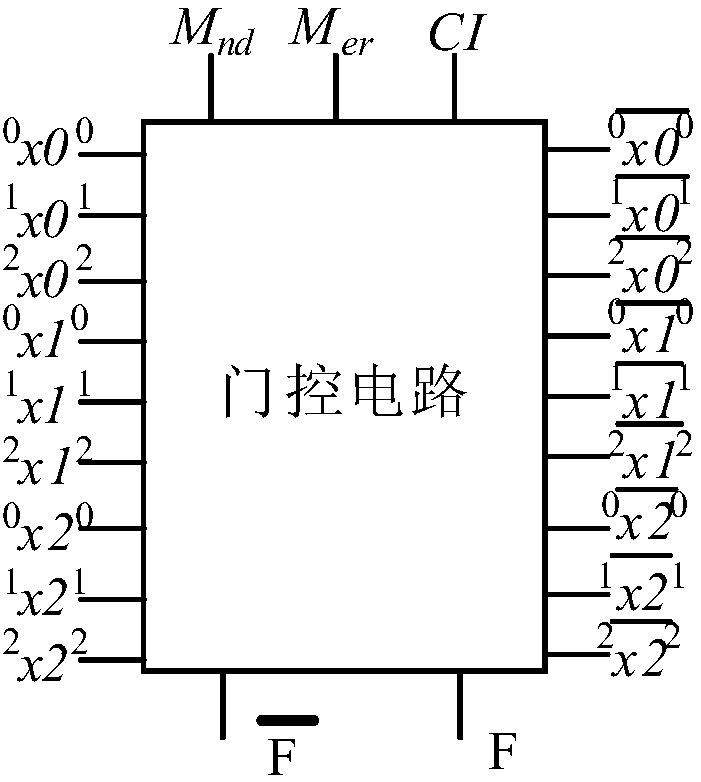

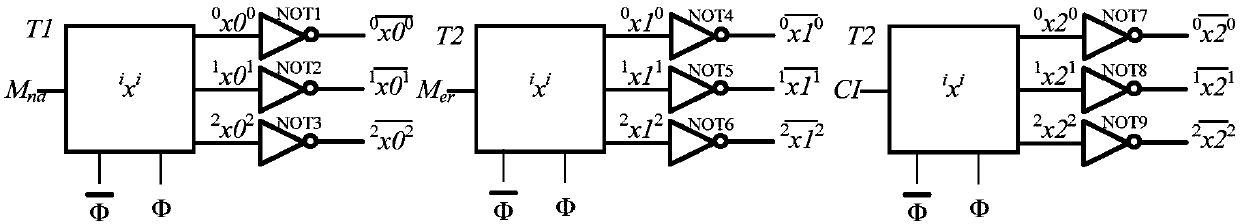

[0025] Embodiment one: if figure 1 , Figure 2(a) and Image 6 As shown, a multi-valued adiabatic multiplier unit circuit based on the transmission gate structure includes a gate control circuit 1, a potential product circuit 2 and a carry circuit 3, and the gate control circuit 1 has a first input terminal, a second input terminal, a third input terminal, first output terminal, second output terminal, third output terminal, fourth output terminal, fifth output terminal, sixth output terminal, seventh output terminal, eighth output terminal, ninth output terminal, first Inversion output terminal, second inversion output terminal, third inversion output terminal, fourth inversion output terminal, fifth inversion output terminal, sixth inversion output terminal, seventh inversion output terminal, eighth inversion output terminal phase output terminal, ninth inverting output terminal, clock control clock signal input terminal and power clock signal input terminal; this volume pro...

Embodiment 2

[0031] Embodiment 2: This embodiment is basically the same as the embodiment, the difference is that in this embodiment, such as Figure 7 As shown, the two-input AND gate AND1 includes a thirty-seventh PMOS transistor P37, a thirty-eighth PMOS transistor P38, a thirty-ninth PMOS transistor P39, a thirty-seventh NMOS transistor N37, a thirty-eighth NMOS transistor N38, and a thirty-eighth NMOS transistor N38. The thirty-ninth NMOS transistor N39, the source of the thirty-seventh PMOS transistor P37, the source of the thirty-eighth PMOS transistor P38 and the source of the thirty-ninth PMOS transistor P39 are all connected to the power supply, the thirty-seventh PMOS transistor The gate of P37 is connected to the gate of the thirty-seventh NMOS transistor N37 and its connection end is the first input end of the two-input AND gate AND1, the gate of the thirty-eighth PMOS transistor P38 is connected to the thirty-eighth NMOS transistor N38 and its connection end is the second inp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More