A method and application of chip test socket structure design based on fea simulation

A technology of chip testing and simulation design, applied in CAD circuit design, electronic circuit testing, computer-aided design, etc., can solve problems such as logic errors and propagation delays, reduce signal interference, ensure test accuracy, and save test costs Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

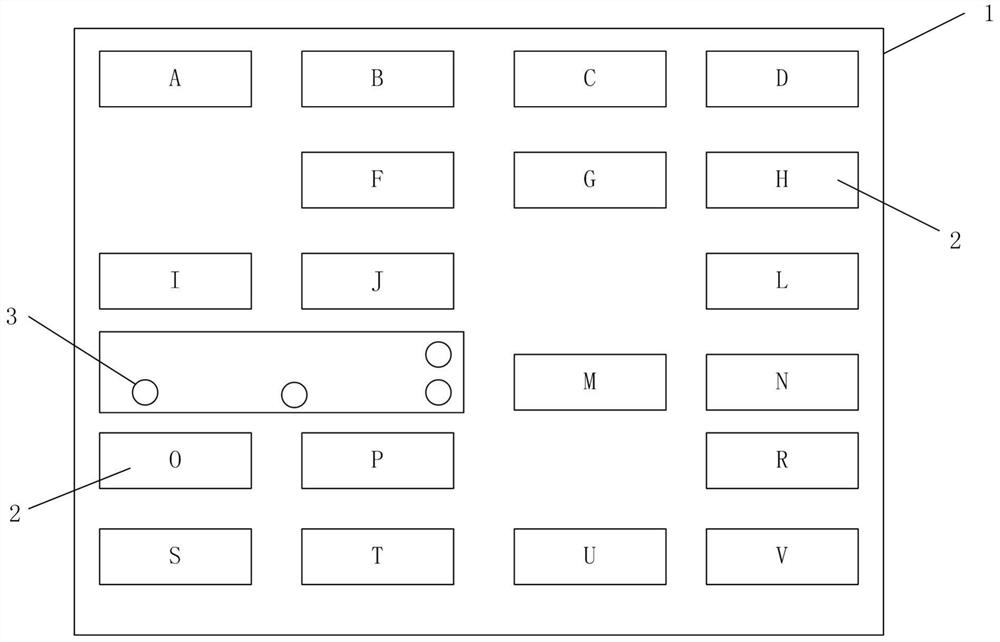

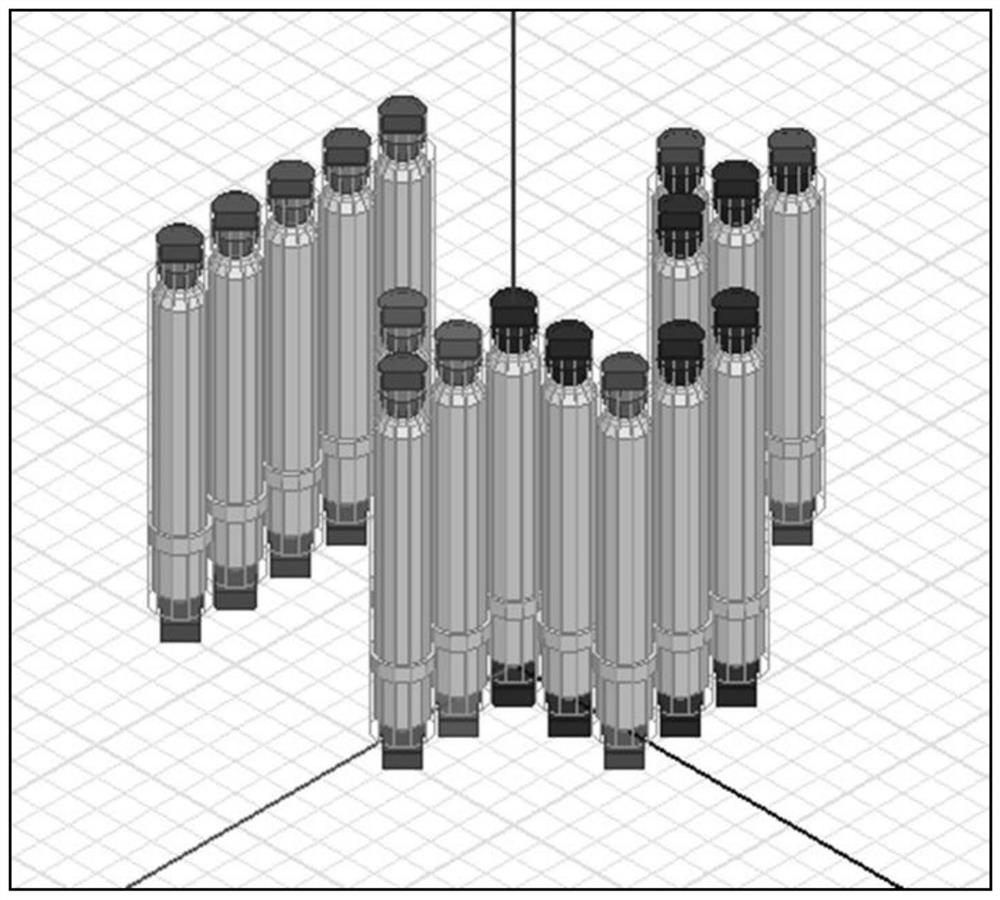

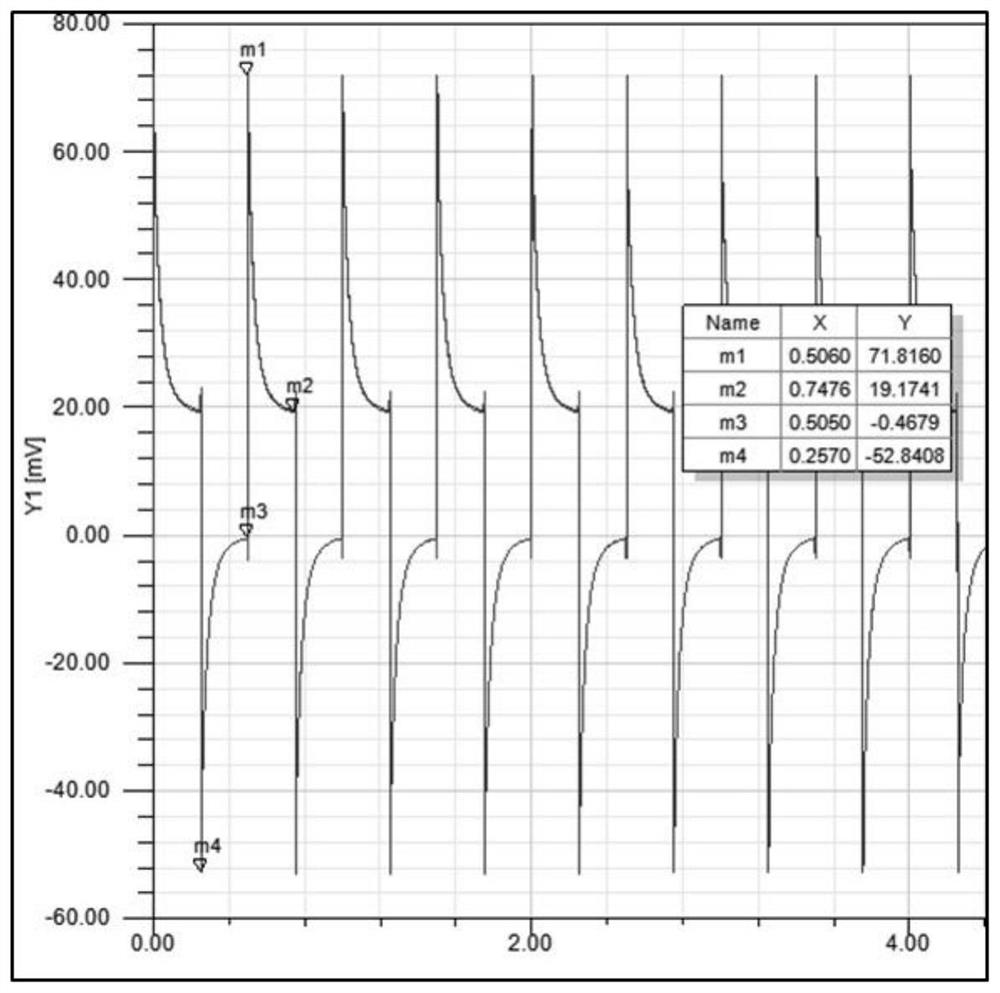

[0030] The technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only part of the embodiments of the present invention, not all of them. to limit the scope of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts fall within the protection scope of the present invention.

[0031] The simulation tool of the present invention is based on Maxwell's equations:

[0032]

[0033]

[0034] ▽·D(r,t)=ρ(r,t)

[0035] ▽·B(r,t)=0

[0036] Among them, E, B, H, D, J and ρ are real variable functions of position (r) and time (t), and the corresponding names and units are as follows:

[0037] H(r,t)——magnetic field density (A / m);

[0038] E(r,t)——electric field strength (V / m);...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More