Chip-size wafer-level scale packaged dynamic random access memory and manufacturing method therefor

A dynamic random, chip size technology, applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, electrical solid-state devices, etc., can solve the problems of increasing the manufacturing cost of dynamic random access memory, power consumption, signal noise, thermal problems, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

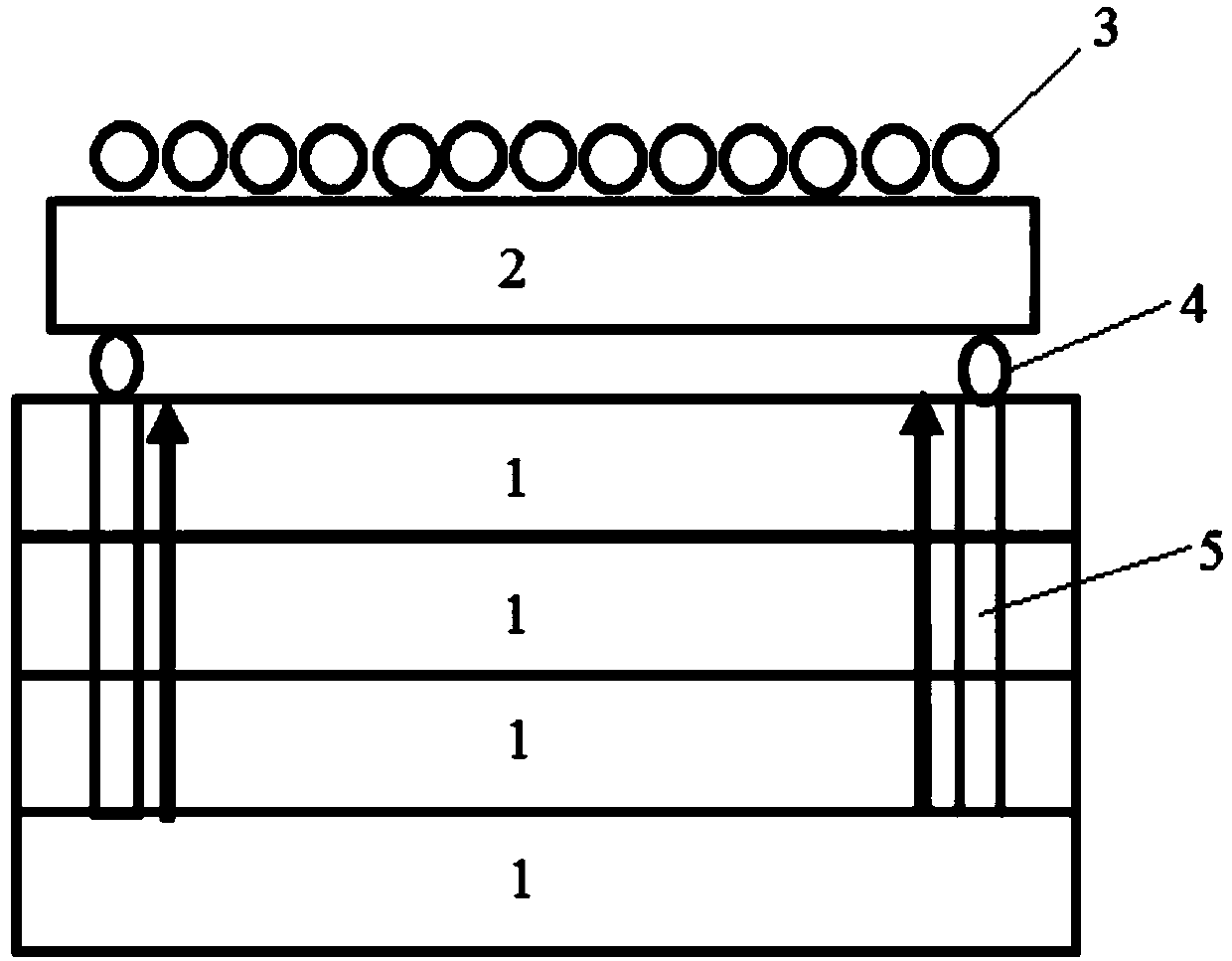

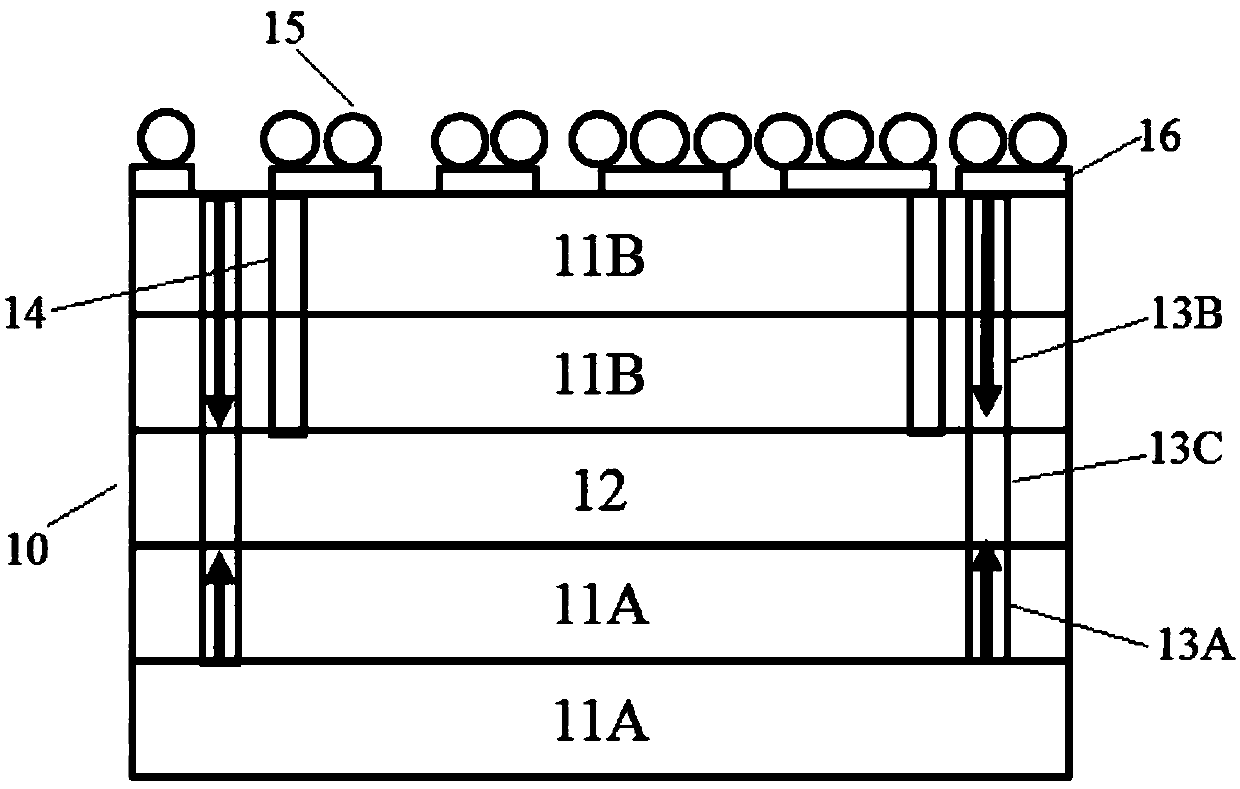

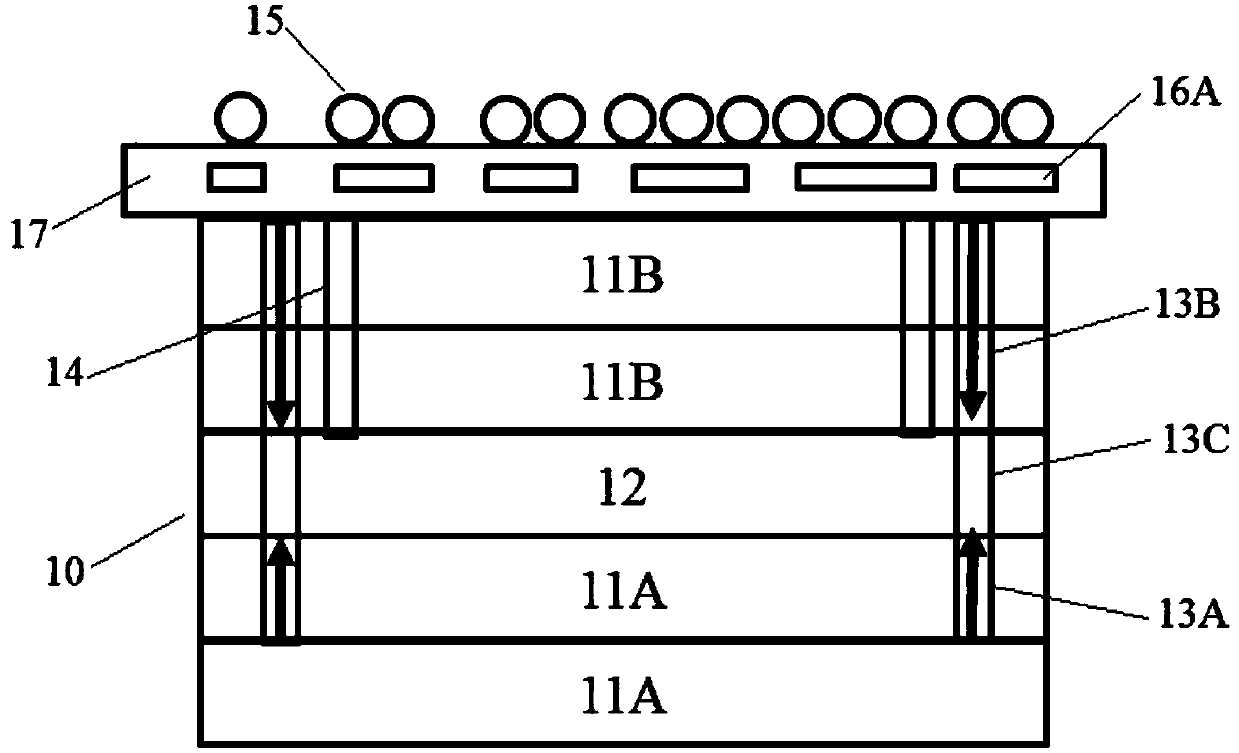

[0056] According to one embodiment of the present invention, the method includes the following steps:

[0057] Step 1, such as Figure 4 and Figure 5 As shown, a plurality of the first main chips 11A are laminated and fixed together, and a first through-silicon via 13A is provided on the first main chip 11A;

[0058] Step two, such as Figure 6 and Figure 7 As shown, the control chip 12 is stacked and fixed above the plurality of first main chips 11A, and a third through-silicon via 13C is provided on the control chip 12;

[0059] Step three, such as Figure 8 to Figure 10 As shown, a plurality of second main chips 11B are stacked and fixed layer by layer above the control chip 12, and second through-silicon vias 13B are provided on the second main chip 11B,

[0060] Wherein, the method further includes connecting the second through-silicon vias 13B of the adjacent second main chip 11B to each other and communicating with the control chip 12; making the first through-si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com