Preparation method of SOI (Silicon-On-Insulator) substrate material

A technology of silicon substrates and silicon substrates, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problems of low surface resistivity of substrates, affecting device performance, and easy introduction of impurities Effects of RF substrate loss, increasing linear characteristics, and suppressing surface parasitic conductance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0039] The present embodiment provides a kind of preparation method of SOI silicon substrate, and this substrate refers to the SOI substrate sheet with doped polycrystalline or doped amorphous silicon layer, and its preparation comprises the following steps:

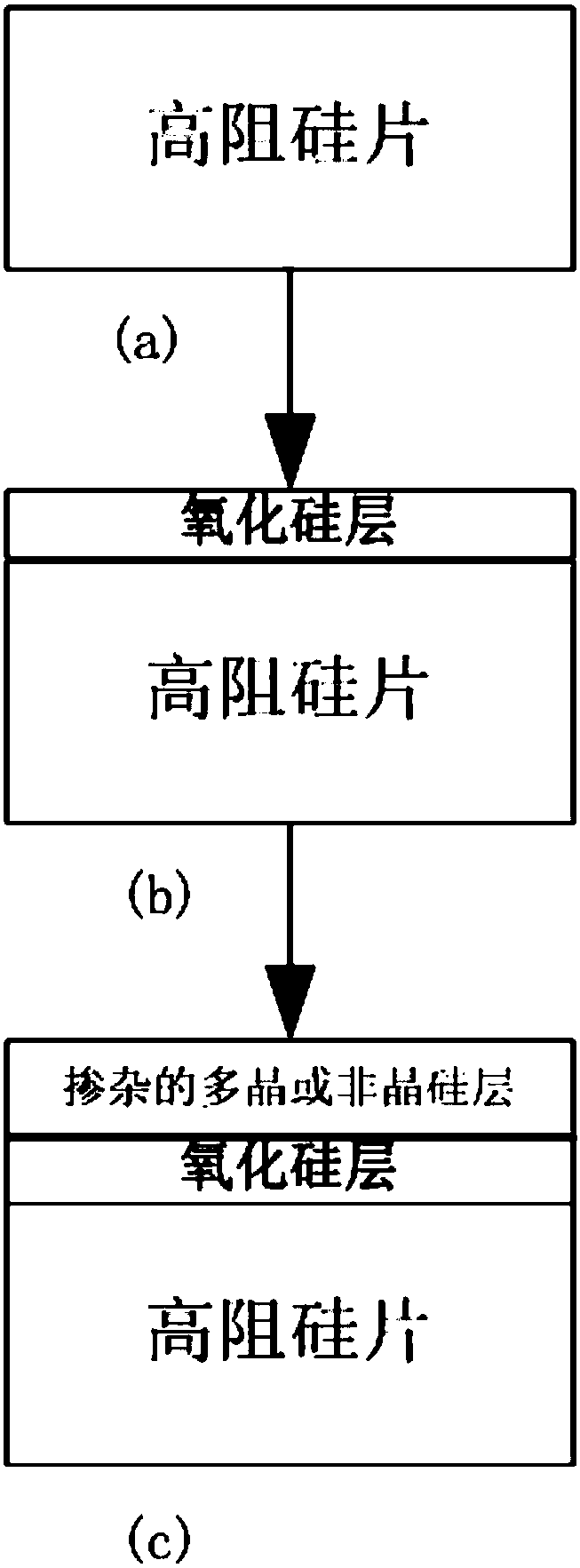

[0040] 1. Provide high-resistance silicon wafers (silicon wafer resistivity greater than 500ohm.cm), and use DHF, SC1 and SC2 to clean the surface in order to remove the natural oxide layer and pollutants on the silicon wafer surface ( figure 1 (a)).

[0041] 2. Reference figure 1 (b), prepare a silicon oxide layer on the surface of the high-resistance silicon wafer, and the thickness of the grown oxide layer is 200A;

[0042] 3. In figure 1 On the basis of (b), prepare a doped polysilicon layer ( figure 1 (c)), the thickness is 2 μm, the doping type is P type, and the resistivity is 1ohm.cm.

[0043] 4. Use figure 1 (c) The formed silicon substrate is formed by using "TM-SOI intelligent cutting method" to form SOI....

Embodiment 2

[0046] This embodiment provides a method for preparing an SOI silicon substrate, which refers to an SOI substrate sheet with a doped polycrystalline or doped amorphous silicon layer, and its preparation includes the following steps:

[0047] 1. Provide high-resistance silicon wafers (silicon wafer resistivity greater than 500ohm.cm), and use DHF, SC1 and SC2 to clean the surface in order to remove the natural oxide layer and pollutants on the silicon wafer surface ( figure 1 (a)).

[0048] 2. Reference figure 1 (b), prepare a silicon oxide layer on the surface of the high-resistance silicon wafer, and the thickness of the grown oxide layer is 200A;

[0049] 3. In figure 1 On the basis of (b), prepare a doped polysilicon layer ( figure 1 (c)), the thickness is 2 μm, the doping type is N type, and the resistivity is 10ohm.cm. .

[0050] 4. Use figure 1 (c) The formed silicon substrate is formed by using the "TM-SOI intelligent cutting method" to form SOI.

[0051] 5. CPW ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More