Interpolation-based model checking path reduction method and computer

一种模型检测、插值的技术,应用在计算、错误检测/纠正、软件测试/调试等方向,能够解决验证崩溃、细化次数多、消耗等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

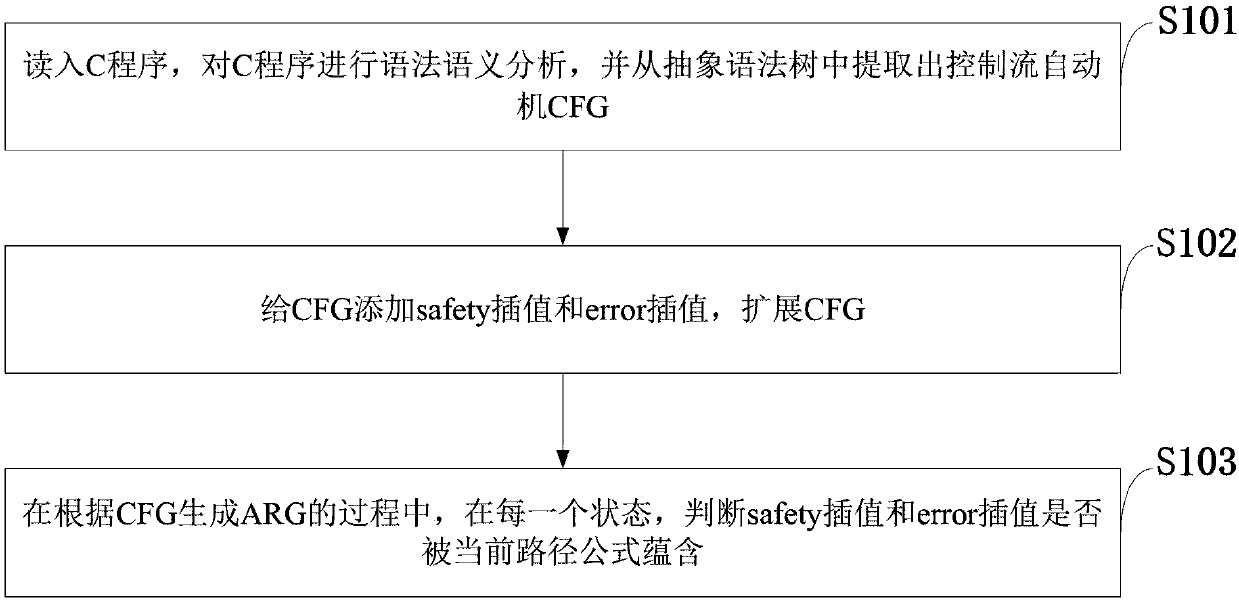

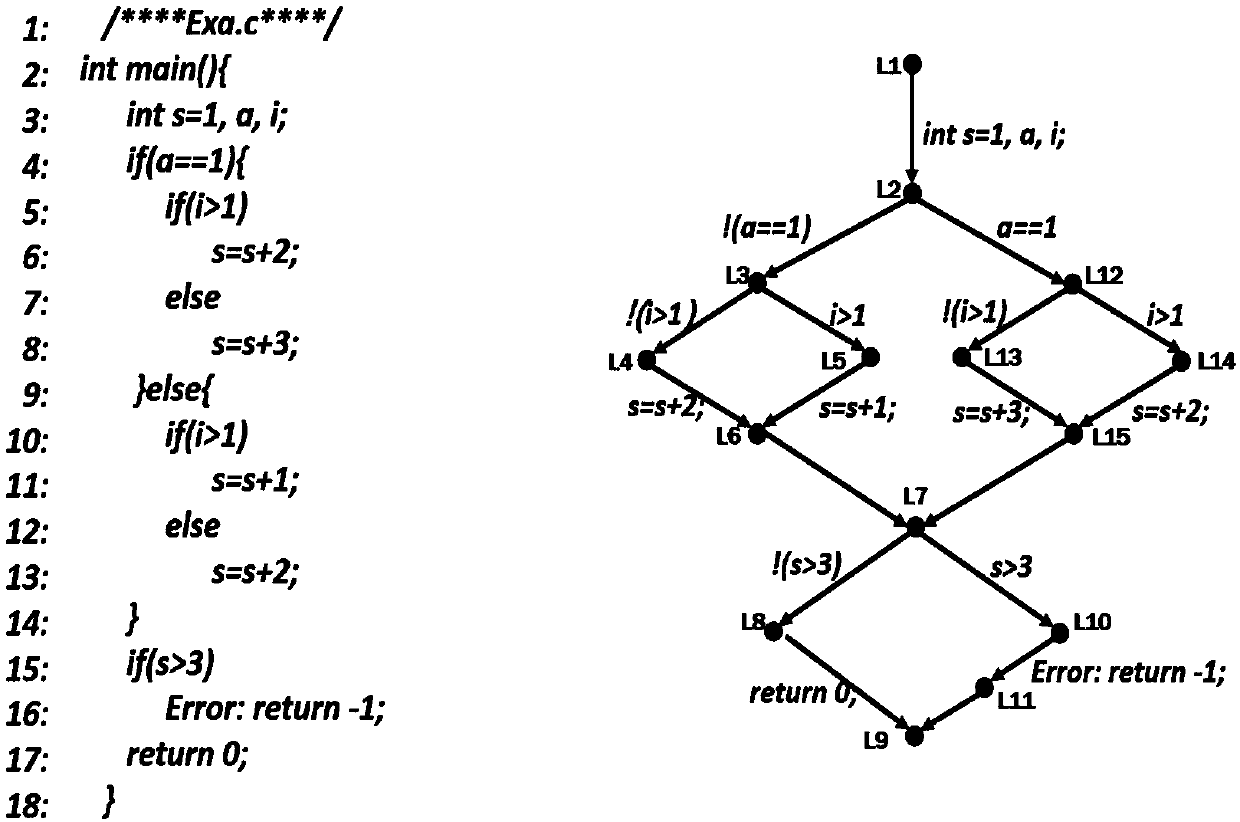

[0121] figure 2 It is the program to be tested and its CFG in Embodiment 1, wherein the target node is L11, and the terminal point is L9. Verify whether the program is safe by verifying the reachability of the target node L11. If L11 is reachable, the program is not safe. Otherwise, the program is safe. The specific verification steps are as follows:

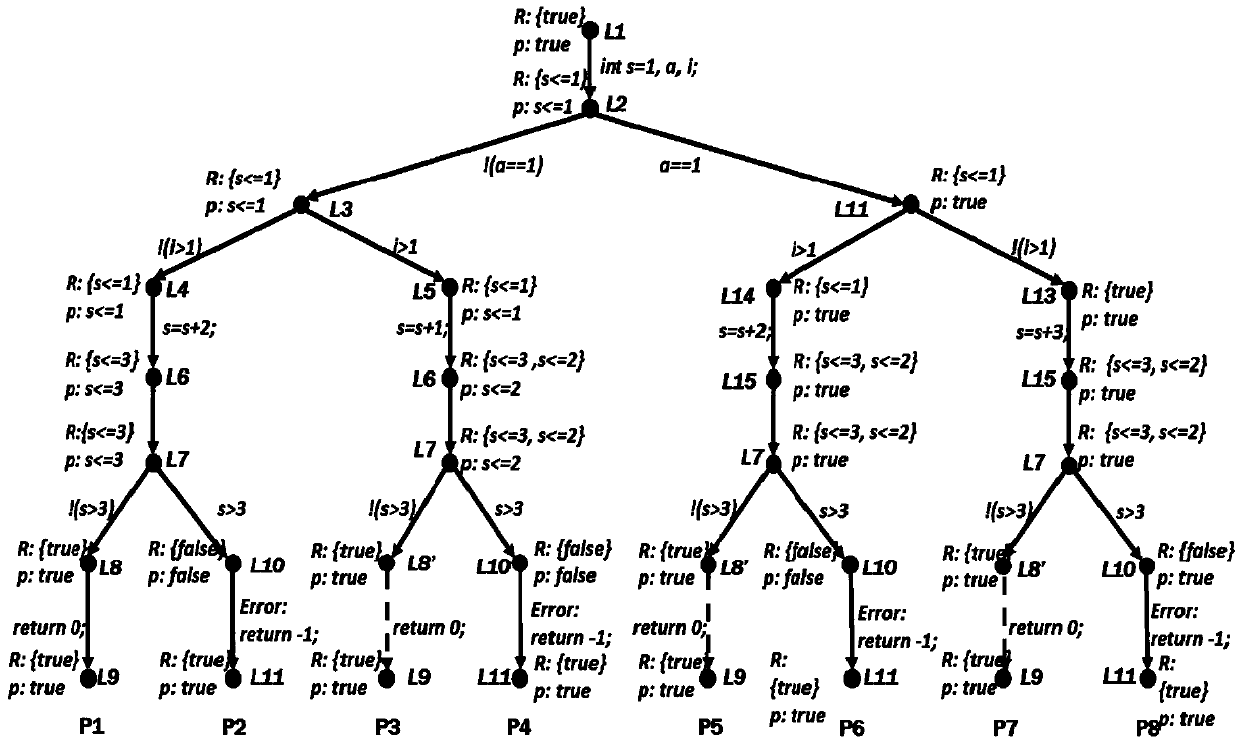

[0122] The realization of the present invention is based on the abstract model detection of CEGAR, which judges the accessibility of a state through the abstract predicate, that is, R interpolation, thereby continuously carrying out the process of counterexample-refinement-abstract, and accurately verifying the program. In order to illustrate the difference and advantages between the interpolation proposed by the present invention and R interpolation, the detection process using only R interpolation is introduced first. image 3 is the path traversed by the verification program using only R interpolation without using S int...

Embodiment 2

[0154] Figure 9 It is the program to be tested and its CFG in Embodiment 2, wherein the target node is L13, and the end point is L4. Verify whether the program is safe by verifying the reachability of the target node L13. If L13 is reachable, the program is not safe. Otherwise, the program is safe. Figure 10 Shows the path traversed using the W value. The specific steps are as follows:

[0155] Step 1: Crop CFG, remove useless edges and nodes, indicated by dotted lines. The process of initializing the properties of the nodes is the same as that in Embodiment 1. At the same time, the W value of all sides is ⊥.

[0156] Step 2: Same as in Embodiment 1, use three kinds of interpolation to expand CFG to generate ARG. Until the first counterexample path P1 is found, such as Figure 10 (1), calculate three kinds of interpolation. Also calculate the W value of the edge. Since L10 is not reachable in P1, but L8 is reachable, the calculation starts from edge e:(L7, a=2, L8)...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More