Three dimensional integrated photon chip interlayer coupler

A photonic chip and three-dimensional integration technology, applied in the coupling of optical waveguides, etc., can solve the problems of diffraction efficiency limitation, difficult to achieve interlayer coupling, etc., and achieve high advantages and feasibility, compact design scheme, and large feature size.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

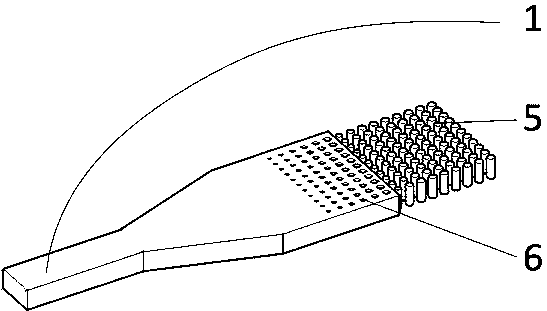

[0018] like figure 1 As shown, 1 and 2 are the optical waveguide layers located in the lower layer in the three-dimensional integrated photonic chip, and 3 are the optical waveguide layer located in the upper layer in the three-dimensional integrated photonic chip, figure 1 The low refractive index medium between the middle waveguide layers is not shown, and 4 is the coupling area between the waveguide layers of the three-dimensional integrated photonic chip of the present invention. In the region 4 of this schematic diagram, by processing a sub-wavelength two-dimensional grating on the waveguide 1 with a high refractive index, the refractive index of the waveguide 1 and the waveguide 3 are matched, and the light can be transmitted from the lower waveguide 1 through evanescent wave coupling. High-efficiency coupling to the upper waveguide 3.

[0019] figure 2 It is a schematic structural diagram of the two-dimensional grating of the interlayer coupler of the present inventi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More