Biaser and manufacturing method thereof

A manufacturing method and biaser technology, applied in semiconductor/solid-state device manufacturing, inductors, capacitors, etc., can solve problems such as inability to completely eliminate the influence of series resonance, uneven broadband, etc., and achieve freedom of choice, large inductance density, Effect of Reducing Parasitic Capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

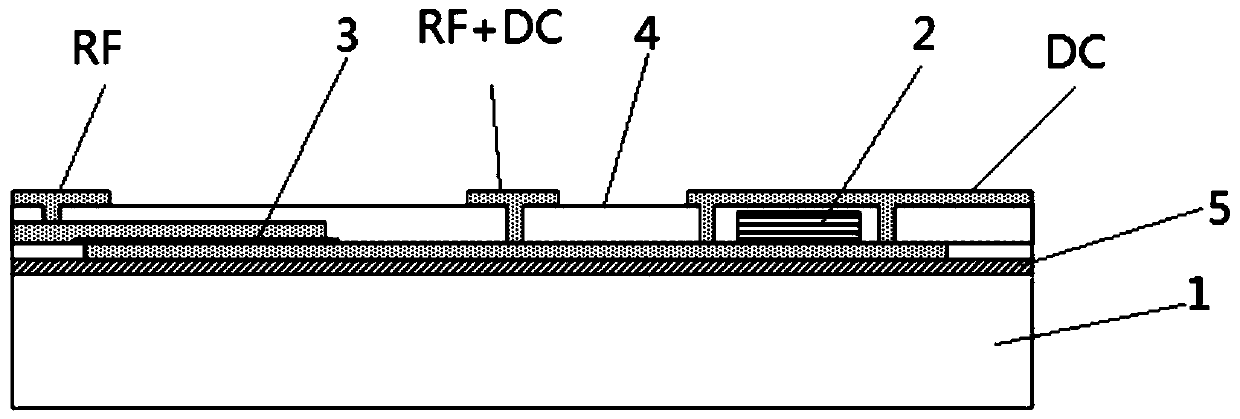

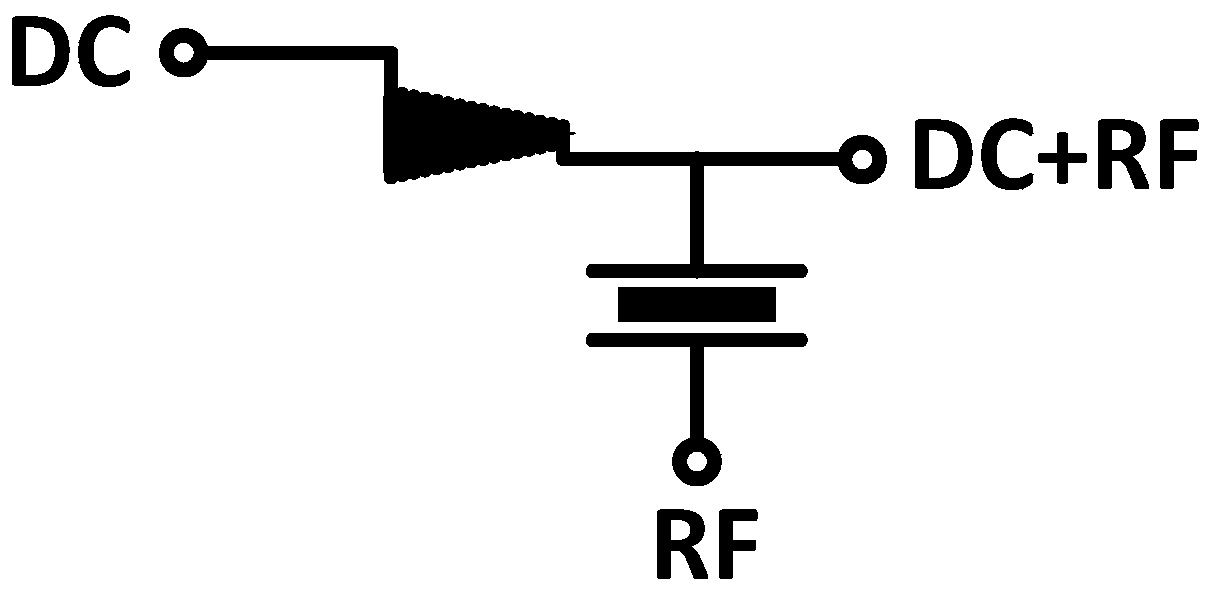

[0050] The embodiment of the present invention provides a bias device, which can be applied to various circuits and systems requiring AC and DC isolation. like figure 1 As shown, the bias device mainly includes: a wafer substrate 1 , an inductor part 2 , a capacitor part 3 and a first insulating layer 4 .

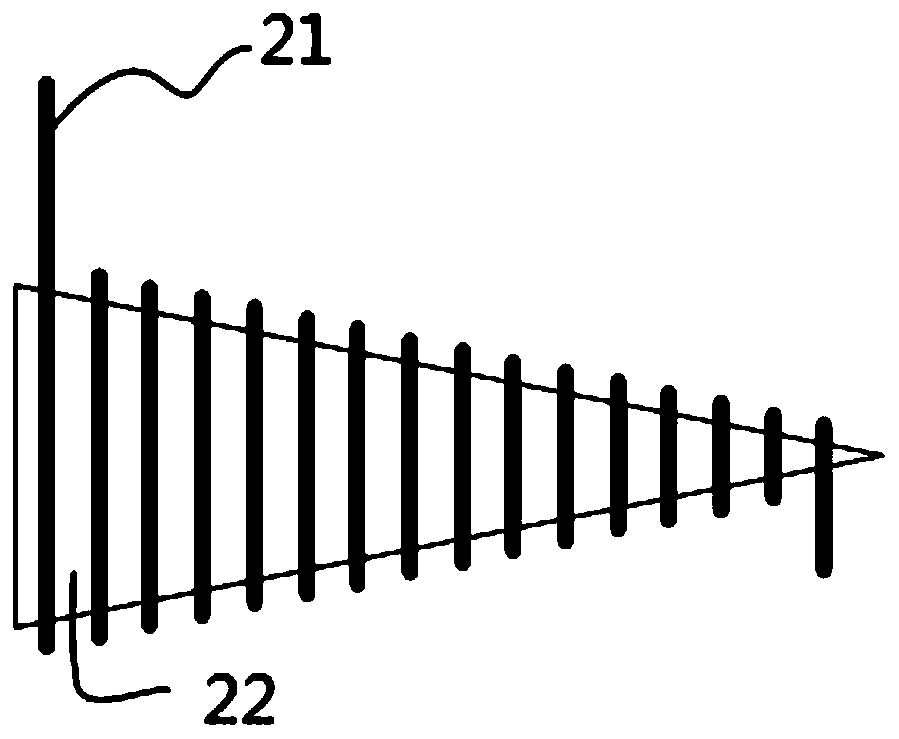

[0051] Wherein, the above-mentioned inductor part 2 and capacitor part 3 are arranged on the wafer substrate 1 . In a preferred embodiment, the inductor part 2 is a tapered inductor, such as figure 2 As shown, the inductance part 2 includes: a wound coil 21 and a conical thin-film magnetic core 22, the wound coil 21 is evenly wound on the conical thin-film magnetic core 22; the wound coil 21 is generally made of high conductivity material, such as copper. The tapered thin-film magnetic core 22 is generally made of high-frequency ferrite or high-performance magnetic thin-film materials such as CoZrTa, CoZrTaB, and CoZrO.

[0052] The first insulating layer 4 covers the waf...

Embodiment 2

[0057] An embodiment of the present invention provides a method for manufacturing a bias device, such as Figure 4 shown, including the following steps:

[0058] Step S1: if Figure 5 As shown, a second insulating layer 5 is formed on the surface of the wafer substrate 1 .

[0059] Step S2 : forming an inductance part 2 and a capacitor part 3 on the wafer substrate 1 with a predetermined distance apart, and the inductance part 2 is a tapered inductor.

[0060] In a preferred embodiment, the above-mentioned step S2, the step of forming the inductance part 2 and the capacitance part 3, such as Image 6 shown, including:

[0061] Step S21 : forming the inductor lower layer coil 211 and the capacitor lower electrode plate 31 on the second insulating layer. In the embodiment of the present invention, such as Figure 7 As shown, the inductance lower coil 211 and the capacitor lower electrode plate 31 are formed in the middle part of the second insulating layer 5, and the two si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More