Multi-die higher-order photonic switching structure based on high-density memory

A memory, high-density technology, applied in the field of high-performance computer system interconnection network, can solve problems such as the inability to meet the actual needs of high-level switching

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

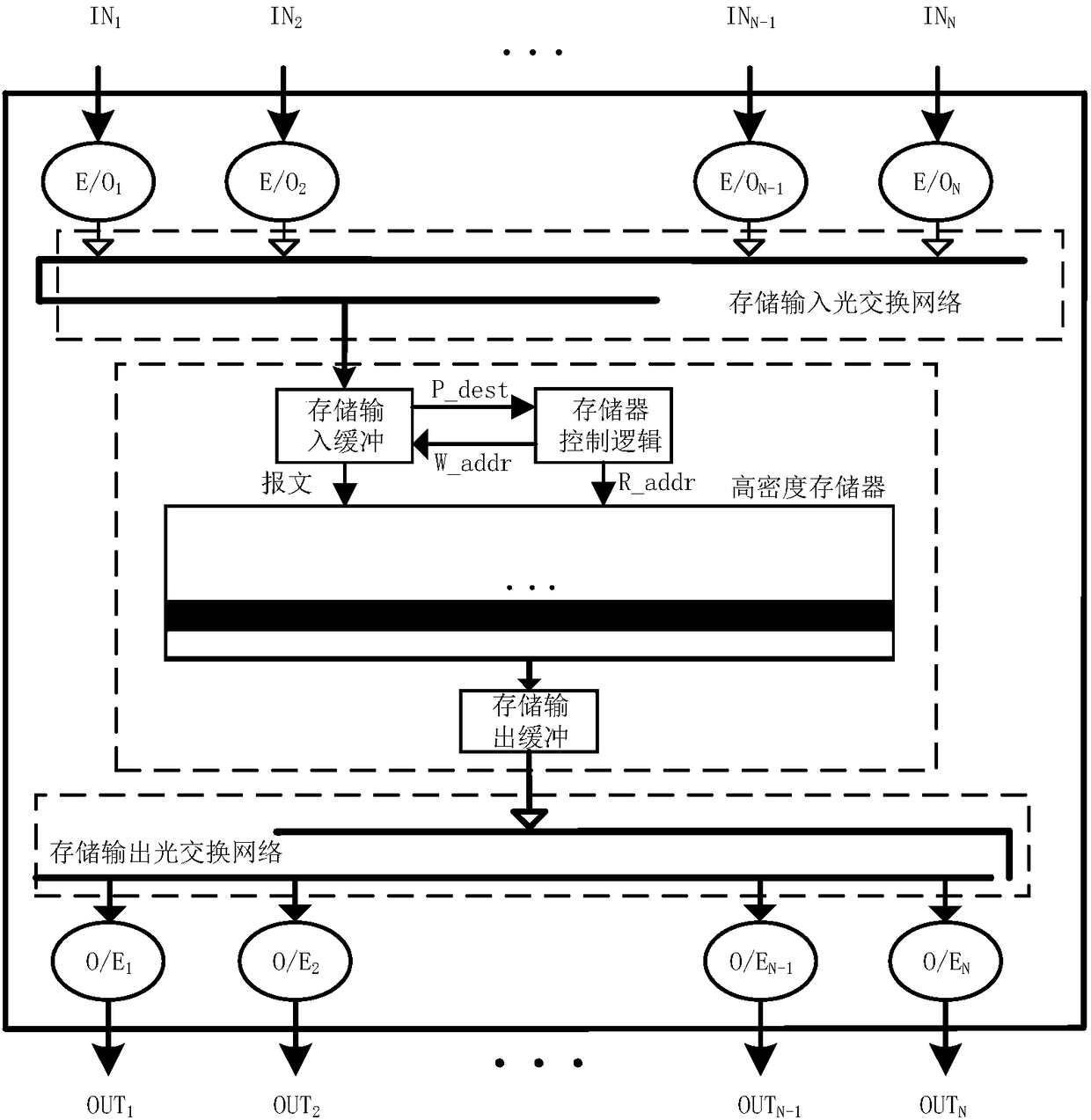

[0065]The previous analysis shows that under the condition of single-port 100Gbps, in order to prevent the high-density memory from becoming the bottleneck of the entire switching network, a single chip can support up to 40 ports to inject packets at a saturated injection rate. When designing the next-generation 64 or even When a high-end switching chip with 128 ports is used, only about 4 memory dies can be realized at most. Although the high connectivity of the fully interconnected network requires each node to provide more ports, when the network scale is small, the number of ports is completely acceptable. On the other hand, due to the point-to-point connectivity characteristics of the fully interconnected network, The number of hops for inter-chip exchange of all messages is only one step. At the same time, the fully interconnected network has features such as deadlock avoidance and livelock avoidance, which greatly simplifies the design of inter-chip routing logic. What ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More