Semiconductor device and manufacture method thereof

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve the problems of small effect, small improvement space, and limited adjustment range of gate polysilicon film deposition temperature, etc., to achieve realization Simple and effective for improving warpage problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0033] In order to improve the wafer warpage problem including multiple grooved IGBT chips, the present invention provides a semiconductor device, which mainly includes:

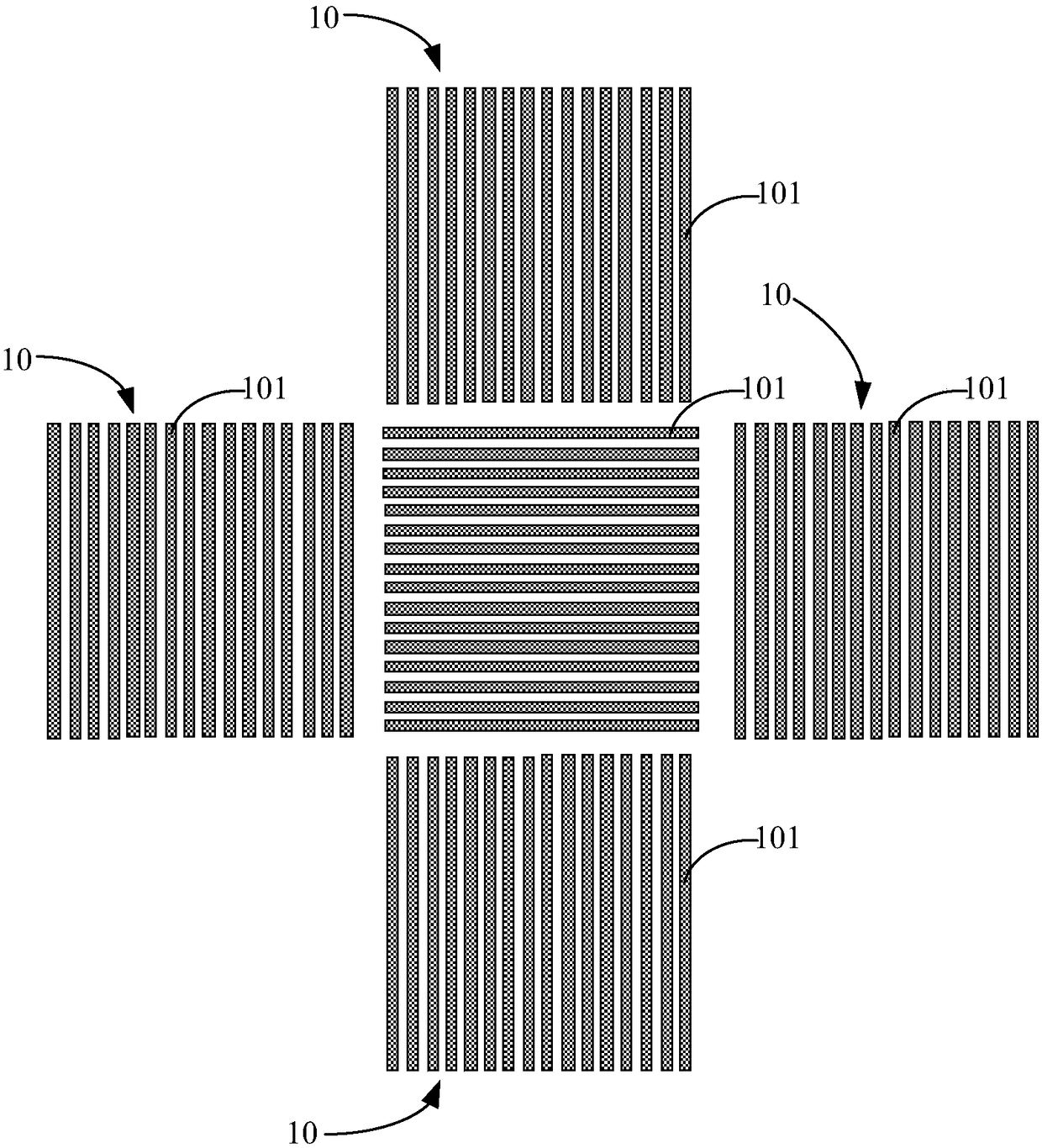

[0034] A wafer, on which a plurality of chips are arranged at intervals, wherein each of the chips includes a plurality of strip-shaped grooves arranged in parallel at intervals, and the strip-shaped grooves in adjacent chips are connected to each other perpendicular to each other.

[0035] The structure of the semiconductor device in the present invention keeps the strip grooves in adjacent chips perpendicular to each other, and the warpage of the wafer caused by the filling of the groove and the gate cancels each other, thereby improving the warpage problem of the whole wafer. At the same time, the conventional gate layer deposition process can also be maintained without any impact on the process, and the implementation is simple.

[0036] Below, refer to figure 1 The semiconductor device structure of th...

Embodiment 2

[0050] In order to solve the foregoing technical problems, the present invention also provides a method for manufacturing a semiconductor device, by which the structure of the semiconductor device in the foregoing implementation 1 can be realized.

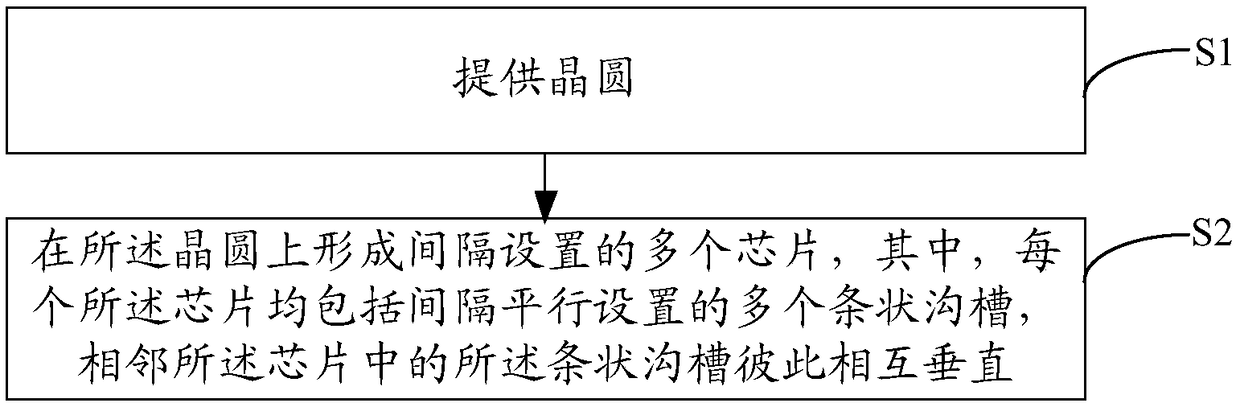

[0051] The manufacturing method of semiconductor device of the present invention mainly comprises the following steps:

[0052] Step S1, providing a wafer;

[0053] Step S2, forming a plurality of chips arranged at intervals on the wafer, wherein each of the chips includes a plurality of strip-shaped grooves arranged in parallel at intervals, and the strip-shaped grooves in the adjacent chips are perpendicular to each other.

[0054] Below, refer to figure 1 and figure 2 The method for manufacturing the semiconductor device of the present invention will be described in detail.

[0055] Specifically, step 1 is performed to provide a wafer.

[0056] The wafer includes a substrate, which may be at least one of the following mate...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More