Resistance Simulation Device Based on Multiplication Digital-to-Analog Converter

A technology of digital-to-analog converters and analog devices, applied in simulators, improvement of basic electrical components, instruments, etc. Resolution is not high, to achieve the effect of a wide range of analog resistance, fast circuit response, and high resolution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

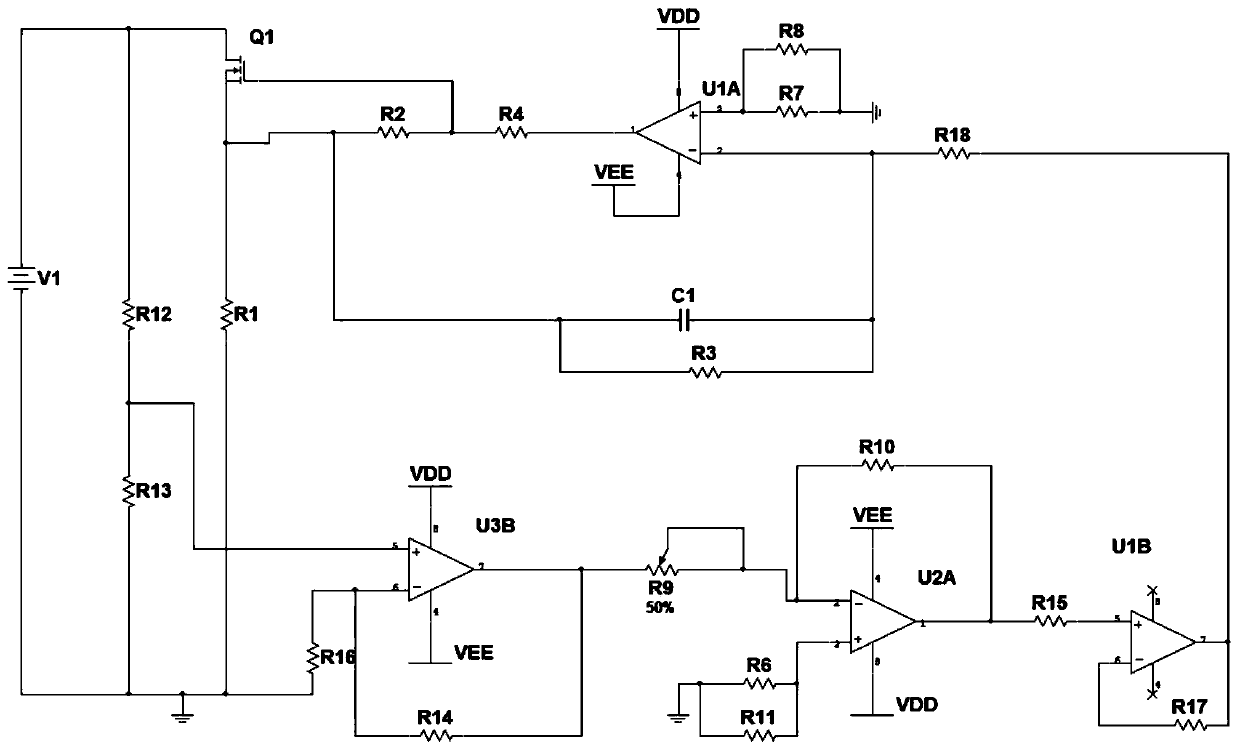

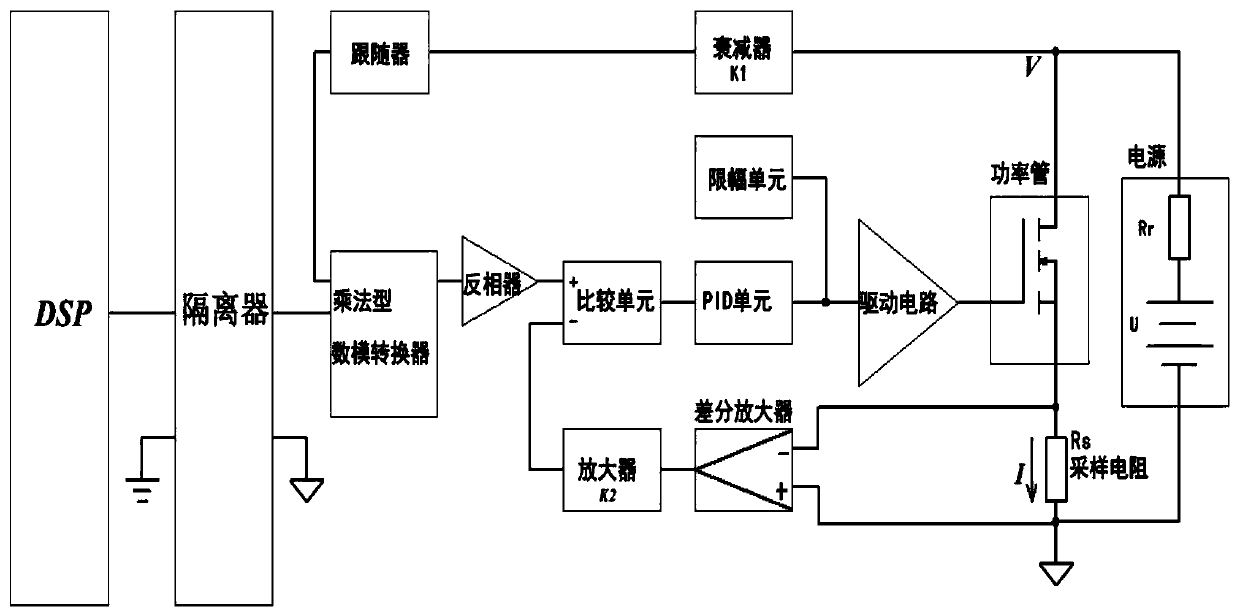

[0020] The present invention will now be further described in conjunction with the accompanying drawings and preferred embodiments. These drawings are all simplified schematic diagrams, which only illustrate the basic structure of the present invention in a schematic manner, so they only show the configurations related to the present invention.

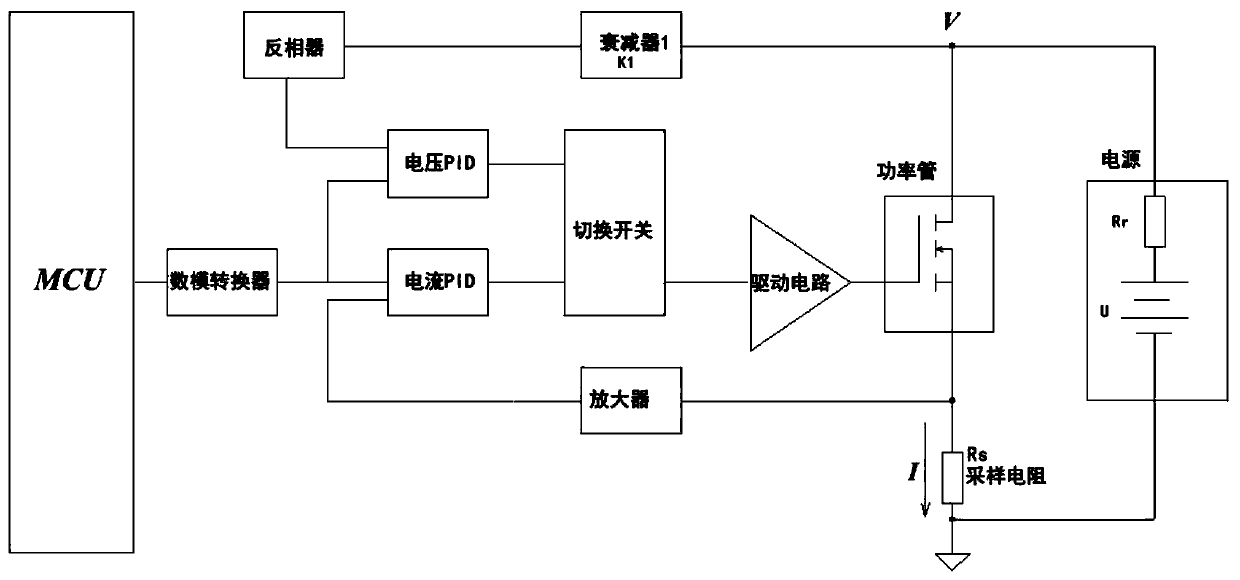

[0021] Such as image 3 As shown, a resistance analog device based on a multiplying digital-to-analog converter in this embodiment includes a digital signal processor DSP, an isolator, a multiplying digital-to-analog converter, an inverter, a comparison unit 3, a PID unit 2, Limiting unit 1, driving circuit 5, power tube, sampling resistor, differential amplifier, amplifier, attenuator, follower, digital ground, analog ground and external test power supply, digital signal processor DSP is connected to the isolator with digital ground as reference On one side, the other side of the isolator is connected to the input terminal of the mu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More