Chip package structure and chip package method

A chip packaging structure and chip packaging technology, applied in electrical components, electrical solid devices, circuits, etc., can solve the problems of low production efficiency and complex chip packaging structure, and achieve high production efficiency, easy industrial preparation, and increased distance. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

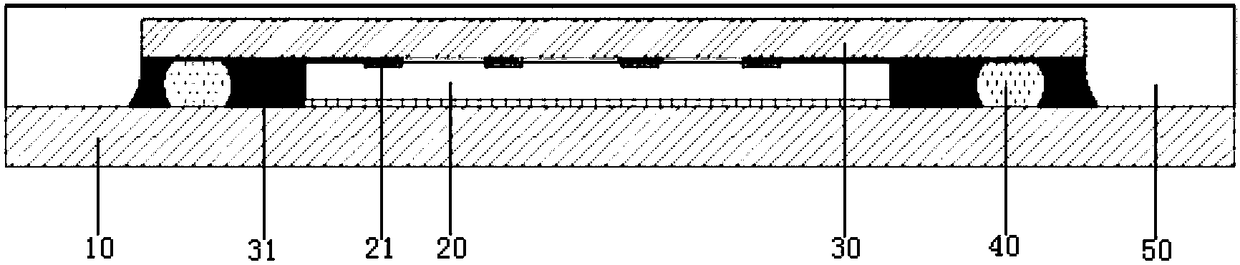

[0044] An embodiment of the present invention provides a chip packaging structure, such as figure 1 As shown, it includes a substrate 10 , and a gold back chip 20 and an interposer 30 sequentially disposed on the substrate 10 . Wherein, the first surface of the gold-backed chip 20 (ie, the gold-backed surface) is electrically connected to the substrate 10 , and the second surface of the gold-backed chip 20 (ie, the front surface, the surface opposite to the gold-backed surface) is electrically connected to the adapter plate 30 .

[0045] By mounting the back gold chip 20 on the adapter plate 30, that is, the back gold chip 20 is arranged between the substrate 10 and the adapter plate 30 and the back gold surface is electrically connected to the substrate 10, and the front side is facing upward, the standard The flip-chip process realizes chip packaging, and the packaging structure is simple, easy for industrial preparation; the preparation efficiency is high, and it is suitabl...

Embodiment 2

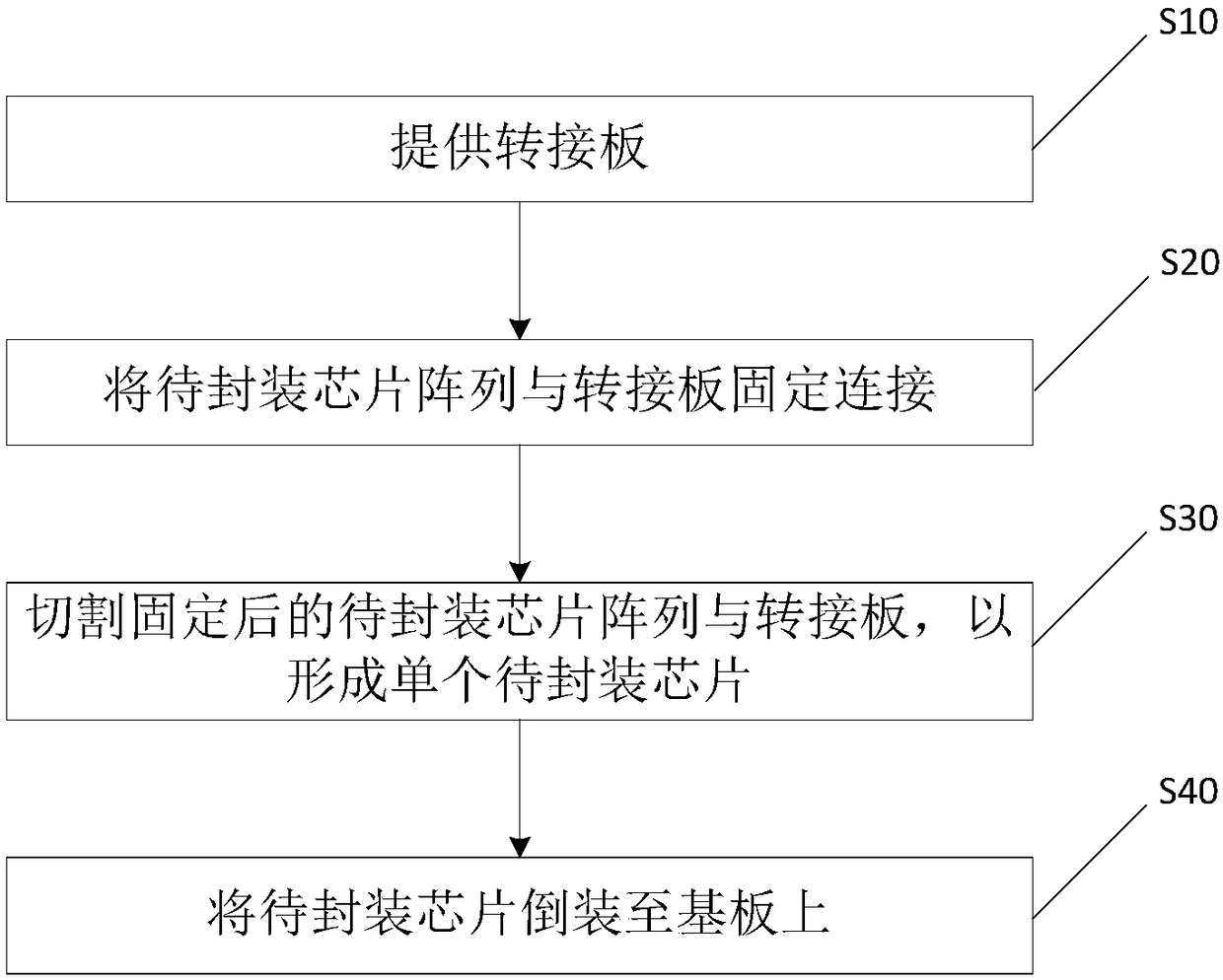

[0057] An embodiment of the present invention provides a chip packaging method, such as figure 2 As shown, the method includes the following steps:

[0058] Step S10, providing an adapter board.

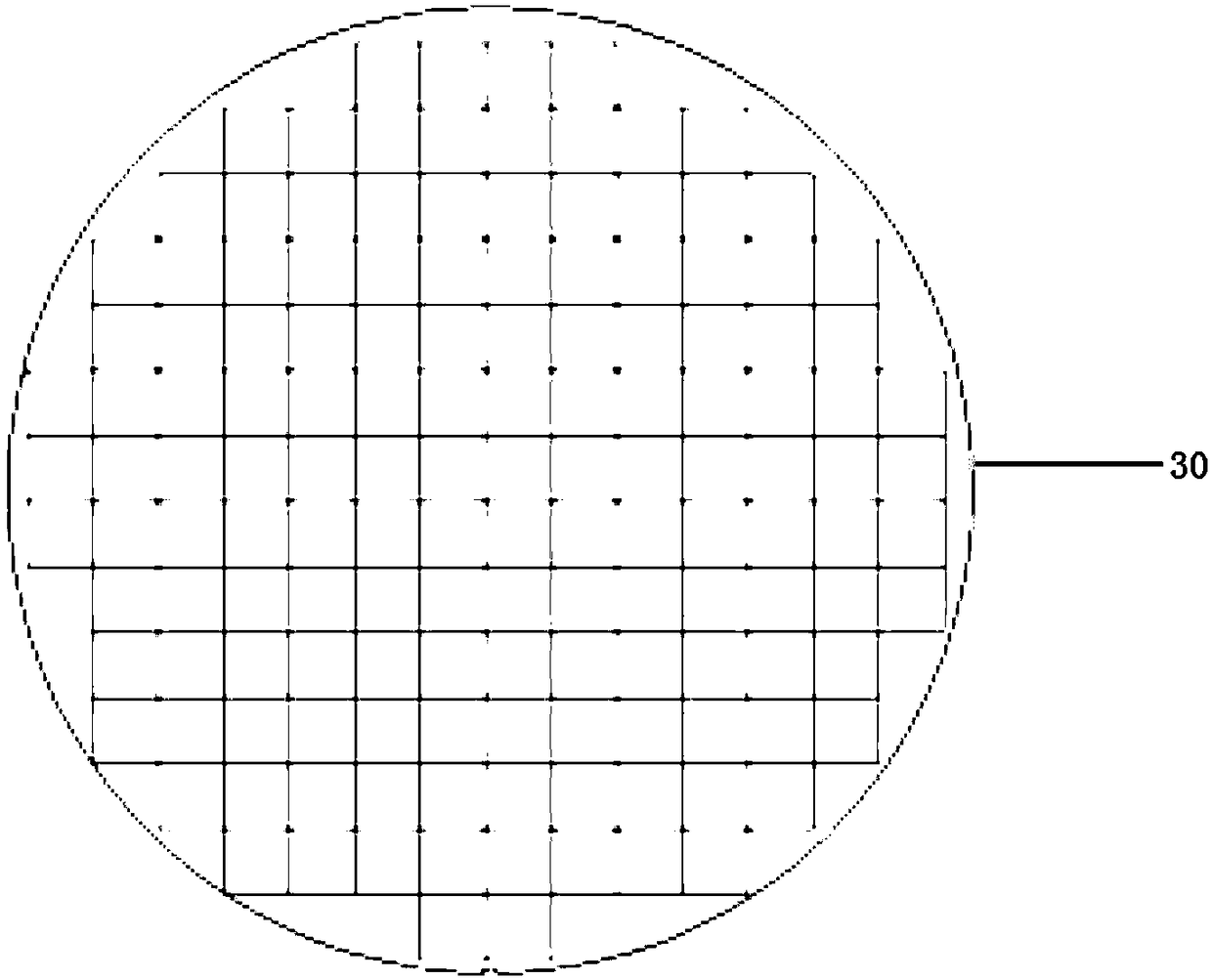

[0059] The adapter plate 30 is a silicon adapter plate, Figure 3a A top view of the interposer 30 is shown, and the subsequent processing technology of the interposer 30 can be realized through a wafer process. Specifically, the following steps are included:

[0060] In step S11 , a redistribution layer 31 is formed on the surface of the interposer board 30 .

[0061] The fabrication of the redistribution layer 31 on the surface of the adapter board 30 is realized through the wafer process, which corresponds to the IO pins on the surface of the chip 20 to be packaged one by one. design.

[0062] Wherein, forming the redistribution layer 31 on the surface of the interposer board 30 may specifically include:

[0063] A metal layer is formed on the surface of the interposer 30, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More