A kind of gan HEMT device and preparation method

A device and gate dielectric layer technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as fluctuations, parasitic parameter changes, and affecting device frequency characteristics, so as to achieve simple operation, improve device frequency characteristics, The effect of reducing process difficulty and cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

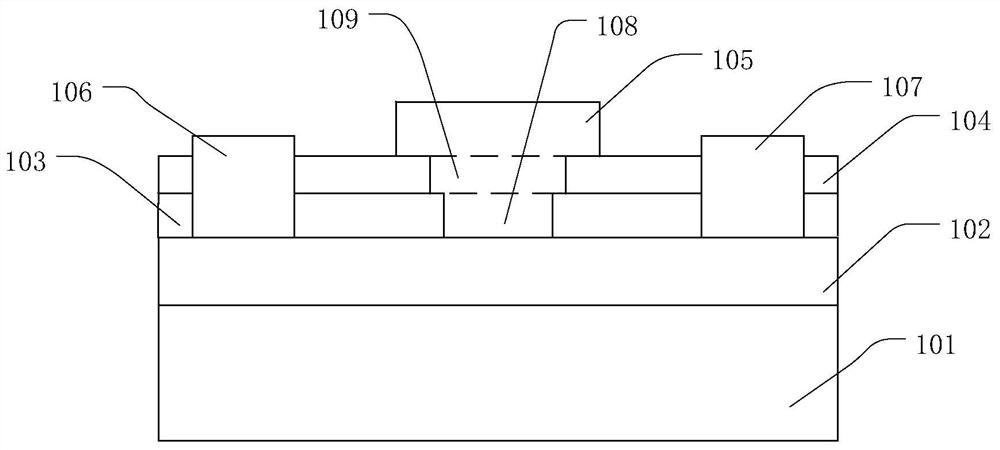

[0045] The GaN HEMT device in this embodiment includes a substrate, and the upper surface of the substrate is sequentially provided with a GaN epitaxial layer and a gate dielectric layer from bottom to top, and also includes a gate, a source electrode and a drain electrode; the gate, The source electrode and the drain electrode penetrate through the gate dielectric layer and are in contact with the GaN epitaxial layer; the gate dielectric layer includes a first gate dielectric layer and a second gate dielectric layer with different properties; A first gate groove that runs through the first gate dielectric layer, and a second gate groove that penetrates the second gate dielectric layer is opened on the second gate dielectric layer; wherein, the positions of the first gate groove and the second gate groove are Corresponding; the gate includes gate metal filling the first gate groove and the second gate groove, and a gate cap arranged on the upper surface of the second dielectric...

Embodiment 2

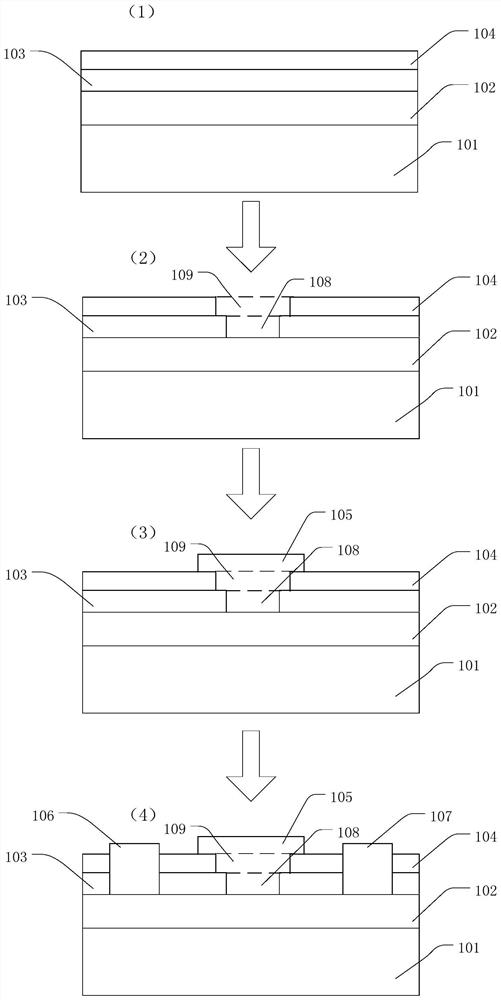

[0051] see figure 2 (1), figure 2 It is a cross-sectional view of the process structure of the preparation method of the GaN HEMT device. The GaN HEMT device includes a substrate 101 , a GaN epitaxial layer 102 , a first gate dielectric layer 103 and a second gate dielectric layer 104 .

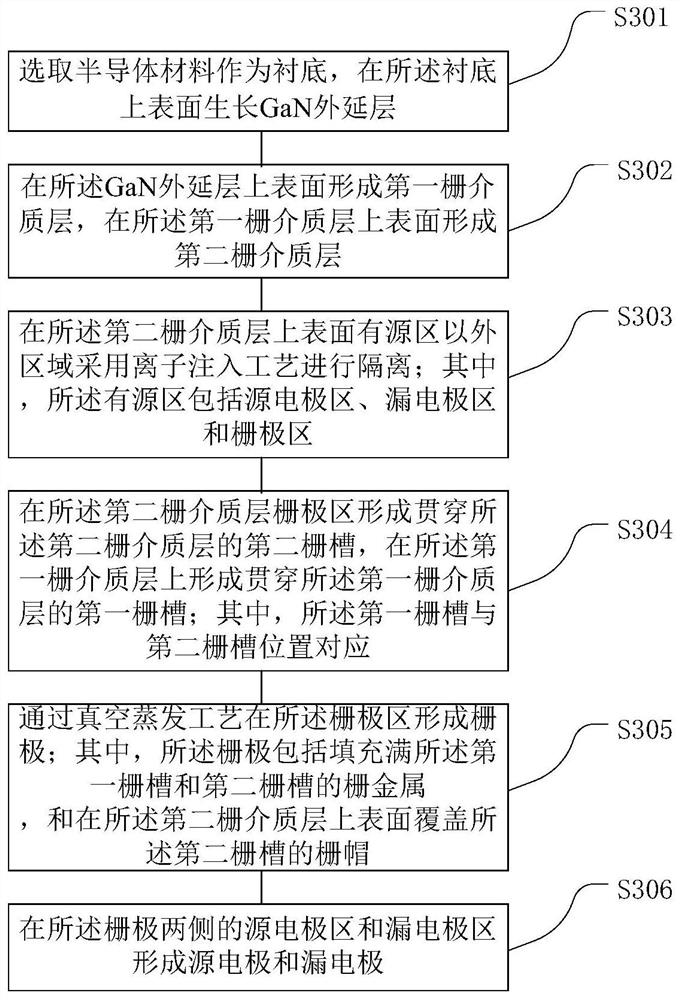

[0052] see image 3 , this embodiment discloses a method for fabricating a GaN HEMT device, which is described in detail as follows:

[0053] In step S301, a semiconductor material is selected as a substrate, and a GaN epitaxial layer is grown on the upper surface of the substrate.

[0054] Optionally, SiC, Si, etc. can be used as the substrate.

[0055] Step S302, forming a first gate dielectric layer on the upper surface of the GaN epitaxial layer, and forming a second gate dielectric layer on the upper surface of the first gate dielectric layer.

[0056] Optionally, the specific implementation method of step S302 is: preparing a first gate dielectric with a thickness of 100nm-200nm ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More